### **MAX2837**

# 2.3GHz to 2.7GHz Wireless Broadband RF Transceiver

### **General Description**

The MAX2837 direct-conversion zero-IF RF transceiver is designed specifically for 2.3GHz to 2.7GHz wireless broadband systems. The MAX2837 completely integrates all circuitry required to implement the RF transceiver function, providing RF-to-baseband receive path; and baseband-to-RF transmit path, VCO, frequency synthesizer, crystal oscillator, and baseband/control interface. The device includes a fast-settling sigma-delta RF synthesizer with smaller than 20Hz frequency steps and a crystal oscillator, which allows the use of a low-cost crystal in place of a TCXO. The transceiver IC also integrates circuits for on-chip DC offset cancellation, I/Q error, and carrier-leakage detection circuits. Only an RF bandpass filter (BPF), crystal, RF switch, PA, and a small number of passive components are needed to form a complete wireless broadband RF radio solution.

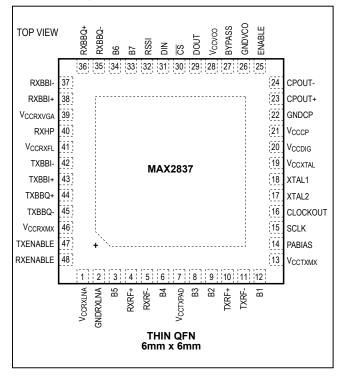

The MAX2837 completely eliminates the need for an external SAW filter by implementing on-chip monolithic filters for both the receiver and transmitter. The baseband filters along with the Rx and Tx signal paths are optimized to meet stringent noise figure and linearity specifications. The device supports up to 2048 FFT OFDM and implements programmable channel filters for 1.75MHz to 28MHz RF channel bandwidths. The transceiver requires only 2µs Tx-Rx switching time, which includes frequency transient settling. The IC is available in a small, 48-pin thin QFN package measuring only 6mm x 6mm x 0.8mm.

### **Applications**

- 802.16-2004 Fixed WiMAX®

- Korea Wibro and 802.16e Mobile WiMAX

- Dual Mode™ WiMAX/802.11b/g Wi-Fi

- Proprietary Wireless Broadband Systems

- 4G/LTE Systems

#### **Features**

- 2.3GHz to 2.7GHz Wideband Operation

- Complete RF Transceiver, PA Driver, and Crystal Oscillator

- · 0dBm Linear OFDM Transmit Power

- -70dBr Tx Spectral Emission Mask

- · 2.3dB Rx Noise Figure

- Tx/Rx I/Q Error and LO Leakage Detection

- Monolithic Low-Noise VCO with -39dBc Integrated Phase Noise

- Programmable Tx I/Q Lowpass Anti-Aliasing Filter

- Sigma-Delta Fractional-N PLL with 20Hz Step Size

- · 45dB Tx Gain-Control Range

- · 94dB Receive Gain-Control Range

- 60dB Analog RSSI Instantaneous Dynamic Range

- · 4-Wire SPI Digital Interface

- I/Q Analog Baseband Interface

- · Digitally Tuned Crystal Oscillator

- · On-Chip Digital Temperature Sensor Read-Out

- +2.7V to +3.6V Transceiver Supply

- Low-Power Shutdown Current

- Small 48-Pin Thin QFN Package (6mm x 6mm x 0.8mm)

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX2837ETM+TD | -40°C to +85°C | 48 TQFN-EP* |

<sup>\*</sup>EP = Exposed pad.

Pin Configuration appears at end of data sheet.

Dual Mode is a trademark of Maxim Integrated Products, Inc. WiMAX is a registered certification mark and registered service mark of the WiMAX Forum.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Absolute Maximum Ratings**

| V <sub>CCLNA</sub> , V <sub>CCTXMX</sub> , V <sub>CCTXPAD</sub> , V <sub>CCDIG</sub> , V <sub>CCCP</sub> , V <sub>CCXTAL</sub> , |

|----------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCVCO</sub> , V <sub>CCRXVGA</sub> , V <sub>CCRXFL</sub> and V <sub>CCRXMX</sub> to                                       |

| GND0.3V to +3.9V                                                                                                                 |

| B1-B7, TXRF_, CS, SCLK, DIN, DOUT, TXBBI_, TXBBQ_,                                                                               |

| RXHP, RXBBI_, RXBBQ_, RSSI, ENABLE, BYPASS,                                                                                      |

| CPOUT_, CLOCKOUT, XTAL1, XTAL2, RXRF_,RXENABLE,                                                                                  |

| TXENABLE to GND0.3V to (Operating V <sub>CC</sub> + 0.3V)                                                                        |

| RXBBI_, RXBBQ_, RSSI, BYPASS, CPOUT_, DOUT, CLOCKOUT,                                                                            |

| PABIAS Short-Circuit Duration                                                                                                    |

| RF Input Power+10dBm                                                                                                             |

CAUTION! ESD SENSITIVE DEVICE

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC Electrical Characteristics**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.7V to 3.6V, Rx set to the maximum gain;  $\overline{CS}$  = high, RXHP = SCLK = DIN = low, RSSI and clock output buffer are off, no signal at RF inputs, all RF inputs and outputs terminated into 50Ω, receiver baseband outputs are open; 90mV<sub>RMS</sub> differential I and Q signals applied to I, Q baseband inputs of transmitter in transmit mode,  $f_{REF}$  = 40MHz, registers set to recommended settings and corresponding test mode,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz, and  $T_{A}$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                 | MIN                   | TYP  | MAX  | UNITS |  |

|-----------------------------------------------------------|--------------------------------------------|-----------------------|------|------|-------|--|

| Supply Voltage                                            | V <sub>CC</sub> _                          | 2.7                   |      | 3.6  | V     |  |

|                                                           | Shutdown mode, T <sub>A</sub> = +25°C      |                       | 10   |      | μA    |  |

|                                                           | Standby mode                               |                       | 35   | 45   |       |  |

| Supply Current                                            | Rx mode                                    |                       | 91   | 110  |       |  |

| Supply Current                                            | Tx mode, $T_A = +25^{\circ}C$              |                       | 145  | 170  | mA    |  |

|                                                           | Rx calibration mode                        |                       | 135  | 160  |       |  |

|                                                           | Tx calibration mode                        |                       | 110  | 135  |       |  |

|                                                           | D9:D8 = 00 in A4:A0 = 00100                | 0.85                  | 1.0  | 1.20 |       |  |

| Rx I/Q Output Common-Mode                                 | D9:D8 = 01 in A4:A0 = 00100                |                       | 1.1  |      | V     |  |

| Voltage                                                   | D9:D8 = 10 in A4:A0 = 00100                |                       | 1.2  |      | ]     |  |

|                                                           | D9:D8 = 11 in A4:A0 = 00100                |                       | 1.35 |      |       |  |

| Tx Baseband Input Common-<br>Mode Voltage Operating Range | DC-coupled                                 | 0.5                   |      | 1.2  | V     |  |

| Tx Baseband Input Bias Current                            | Source current                             |                       | 10   | 20   | μA    |  |

| LOGIC INPUTS: ENABLE, TXEN                                | ABLE, RXENABLE, SCLK, DIN, CS, B7:B1, RXHP |                       |      |      |       |  |

| Digital Input-Voltage High, V <sub>IH</sub>               |                                            | V <sub>CC</sub> - 0.4 | 4    |      | V     |  |

| Digital Input-Voltage Low, V <sub>IL</sub>                |                                            |                       |      | 0.4  | V     |  |

| Digital Input-Current High, I <sub>IH</sub>               |                                            | -1                    |      | +1   | μA    |  |

| Digital Input-Current Low, I <sub>IL</sub>                |                                            | -1                    |      | +1   | μA    |  |

### **DC Electrical Characteristics (continued)**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.7V to 3.6V, Rx set to the maximum gain;  $\overline{CS}$  = high, RXHP = SCLK = DIN = low, RSSI and clock output buffer are off, no signal at RF inputs, all RF inputs and outputs terminated into 50Ω, receiver baseband outputs are open; 90mV<sub>RMS</sub> differential I and Q signals applied to I, Q baseband inputs of transmitter in transmit mode, f<sub>REF</sub> = 40MHz, registers set to recommended settings and corresponding test mode, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.8V, f<sub>LO</sub> = 2.5GHz, and T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                    | CONDITIONS     | MIN                  | TYP | MAX | UNITS |

|----------------------------------------------|----------------|----------------------|-----|-----|-------|

| LOGIC OUTPUTS: DOUT                          |                |                      |     |     |       |

| Digital Output-Voltage High, V <sub>OH</sub> | Sourcing 100µA | V <sub>CC</sub> - 0. | 4   |     | V     |

| Digital Output-Voltage Low, V <sub>OL</sub>  | Sinking 100µA  |                      |     | 0.4 | V     |

### **AC Electrical Characteristics—Rx MODE**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{RF}$  = 2.502GHz,  $f_{LO}$  = 2.5GHz; receiver baseband I/Q outputs at 90mV<sub>RMS</sub> (-21dBV),  $f_{REF}$  = 40MHz, ENABLE = RXENABLE =  $\overline{CS}$  = high, TXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode,  $T_A$  = +25°C, unless otherwise noted. Lowpass filter is set to 10MHz RF channel BW. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                                                                                            |                               | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-----|-------|

| RECEIVER SECTION: LNA RF IN                               | PUT TO BASEBAND                                                                                                       | I/Q OUTPUTS                   |     |     |     |       |

| RF Input Frequency Range                                  |                                                                                                                       |                               | 2.3 |     | 2.7 | GHz   |

| Peak-to-Peak Gain Variation over RF Input Frequency Range | Tested at band edges                                                                                                  | and band center               |     | 0.8 |     | dB    |

| RF Input Return Loss                                      | All LNA gain settings                                                                                                 |                               |     | 13  |     | dB    |

| Total Voltage Gain                                        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                   | Maximum gain, B7:B1 = 0000000 | 90  | 99  |     | dB    |

| Total Voltage Gaill                                       | 1A = -40 C to 103 C                                                                                                   | Minimum gain, B7:B1 = 1111111 |     | 5   | 13  | U.D.  |

|                                                           | From max RF gain to                                                                                                   | max RF gain - 8dB             |     | 8   |     |       |

| RF Gain Steps                                             | From max RF gain to                                                                                                   | max RF gain - 16dB            |     | 16  |     | dB    |

|                                                           | From max RF gain to                                                                                                   | max RF gain - 32dB            |     | 32  |     |       |

| Gain Change Settling Time                                 | Any RF or baseband gain change; gain settling to within P1dB of steady state; RXHP = 1                                |                               |     | 0.2 |     |       |

|                                                           | Any RF or baseband gain change; gain settling to within P0.1dB of steady state; RXHP = 1                              |                               |     | 2   |     | ł µs  |

| Baseband Gain Range                                       | From maximum baseband gain (B5:B1 = 00000) to minimum baseband gain (B5:B1 = 11111),  T <sub>A</sub> = -40°C to +85°C |                               | 58  | 62  | 66  | dB    |

| Baseband Gain Minimum<br>Step Size                        |                                                                                                                       |                               |     | 2   |     | dB    |

|                                                           | Voltage gain R 65dB                                                                                                   | with max RF gain (B7:B6 = 00) |     | 2.3 |     |       |

|                                                           | Voltage gain = 50dB (B7:B6 = 01)                                                                                      | with max RF gain - 8dB        |     | 5.5 |     |       |

| DSB Noise Figure                                          | Voltage gain = 45dB with max RF gain - 16dB (B7:B6 = 10)                                                              |                               |     | 17  |     | dB    |

|                                                           | Voltage gain = 15dB with max RF gain - 32dB (B7:B6 = 11)                                                              |                               |     | 27  |     |       |

### **AC Electrical Characteristics—Rx MODE (continued)**

(MAX2837 evaluation kit:  $V_{CC} = 2.8V$ ,  $f_{RF} = 2.502GHz$ ,  $f_{LO} = 2.5GHz$ ; receiver baseband I/Q outputs at  $90mV_{RMS}$  (-21dBV),  $f_{REF} = 40MHz$ , ENABLE = RXENABLE =  $\overline{CS}$  = high, TXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode,  $T_A = +25^{\circ}C$ , unless otherwise noted. Lowpass filter is set to 10MHz RF channel BW. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Note 1)

| PARAMETER                                       | CC                                                                                                                                           | ONDITIONS                                                           | MIN  | TYP  | MAX  | UNITS            |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|------|------|------------------|

|                                                 | Max RF gain (B7:B6 = 00)                                                                                                                     |                                                                     |      | -37  |      |                  |

| In Bond Input D 1dB                             | Max RF gain - 8dB (B7:B6 = 01)                                                                                                               |                                                                     |      | -29  |      | dBm              |

| In-Band Input P-1dB                             | Max RF gain - 16dB (B7:B                                                                                                                     | 6 = 10)                                                             |      | -21  |      | UDIII            |

|                                                 | Max RF gain - 32dB (B7:B                                                                                                                     | 6 = 11)                                                             |      | -4   |      |                  |

| Maximum Output Signal Level                     | Over passband frequency compression point                                                                                                    | range; at any gain setting; 1dB                                     |      | 2.5  |      | V <sub>P-P</sub> |

|                                                 | Max RF gain (B7:B6 = 00) wanted signal                                                                                                       | , AGC set for -65dBm                                                |      | -11  |      |                  |

| Out of Dand Input ID2 (Note 2)                  | Max RF gain - 8dB (B7:B6 wanted signal                                                                                                       | = 01), AGC set for -55dBm                                           |      | -8   |      | dBm              |

| Out-of-Band Input IP3 (Note 2)                  | Max RF gain - 16dB (B7:B wanted signal                                                                                                       | 6 = 10), AGC set for -40dBm                                         |      | -6   |      | иын              |

|                                                 | Max RF gain - 32dB (B7:B6 = 11), AGC set for -30dBm wanted signal                                                                            |                                                                     |      | +16  |      |                  |

| I/Q Phase Error                                 | 50kHz baseband output; 1                                                                                                                     | σ variation                                                         |      | 0.15 |      | Degrees          |

| I/Q Gain Imbalance                              | 50kHz baseband output; 1                                                                                                                     | σ variation                                                         |      | 0.1  |      | dB               |

| Rx I/Q Output Load Impedance                    | Minimum differential resist                                                                                                                  | ance                                                                | 10   |      |      | kΩ               |

| (R    C)                                        | Maximum differential capacitance                                                                                                             |                                                                     |      | 5    |      | pF               |

| I/Q Output DC Droop                             | After switching RXHP to 0; average over 1µs after any gain change, or 2µs after receive enabled with 100Hz interval ACcoupling, 1σ variation |                                                                     |      | ±1   |      | mV/ms            |

| I/Q Static DC Offset                            | No RF input signal; measu<br>RXHP = 1 for 0 to 2μs and<br>1σ variation                                                                       | re at 3µs after receive enable;<br>set to 0 after 2µs,              |      | ±1   |      | mV               |

| Loopback Gain<br>(for Receiver I/Q Calibration) |                                                                                                                                              | ceiver I/Q output; transmitter B6:B1 = 10100 programmed through SPI | -4.5 | 0    | +4.5 | dB               |

| RECEIVER BASEBAND FILTERS                       | 3                                                                                                                                            |                                                                     |      |      |      |                  |

|                                                 | At 15MHz                                                                                                                                     |                                                                     |      | 57   |      |                  |

| Baseband Filter Rejection                       | At 20MHz                                                                                                                                     |                                                                     |      | 75   |      | dB               |

|                                                 | At > 40MHz                                                                                                                                   |                                                                     |      | 90   |      |                  |

|                                                 | RXHP = 1 (used before AC                                                                                                                     | RXHP = 1 (used before AGC completion)                               |      |      |      |                  |

| Baseband Highpass Filter Corner                 | D5:D4 = 00                                                                                                                                   |                                                                     |      | 0.1  |      |                  |

| Frequency                                       | RXHP = 0 (used after AGC completion) address                                                                                                 | D5:D4 = 01                                                          |      | 1    |      | kHz              |

|                                                 | A4:A0 = 01110                                                                                                                                | D5:D4 = 10                                                          |      | 30   |      |                  |

|                                                 | D5:D4 = 11                                                                                                                                   |                                                                     |      | 100  |      |                  |

### **AC Electrical Characteristics—Rx MODE (continued)**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{RF}$  = 2.502GHz,  $f_{LO}$  = 2.5GHz; receiver baseband I/Q outputs at 90mV<sub>RMS</sub> (-21dBV),  $f_{REF}$  = 40MHz, ENABLE = RXENABLE =  $\overline{CS}$  = high, TXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the typical applications and registers set to default settings and corresponding test mode,  $T_A$  = +25°C, unless otherwise noted. Lowpass filter is set to 10MHz RF channel BW. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Note 1)

| PARAMETER                     | С                                      | ONDITIONS                              | MIN 7 | TYP M | AX    | UNITS             |

|-------------------------------|----------------------------------------|----------------------------------------|-------|-------|-------|-------------------|

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 0000                           | 1     | 1.75  |       |                   |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 0001                           | 2     | 2.25  |       |                   |

|                               | A4:A0 = 00010 serial bits              | A4:A0 = 00010 serial bits D7:D4 = 0010 |       |       |       |                   |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 0011                           |       | 5.0   |       |                   |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 0100                           |       | 5.5   |       |                   |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 0101                           |       | 6.0   |       |                   |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 0110                           |       | 7.0   |       |                   |

| RF Channel BW Supported by    | A4:A0 = 00010 serial bits              | D7:D4 = 0111                           |       | 8.0   |       | N41.1-            |

| Baseband Filter               | A4:A0 = 00010 serial bits              | D7:D4 = 1000                           |       | 9.0   |       | MHz               |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 1001                           | 1     | 10.0  |       |                   |

|                               | A4:A0 = 00010 serial bits              | D7:D4 = 1010                           | 1     | 12.0  |       |                   |

|                               | A4:A0 = 00010 serial bits              | 1                                      | 14.0  |       |       |                   |

|                               | A4:A0 = 00010 serial bits              | 1                                      | 15.0  |       |       |                   |

|                               | A4:A0 = 00010 serial bits D7:D4 = 1101 |                                        | 2     | 20.0  |       |                   |

|                               | A4:A0 = 00010 serial bits              | 2                                      | 24.0  |       |       |                   |

|                               | A4:A0 = 00010 serial bits              | 2                                      | 28.0  |       |       |                   |

| Passband Cain Dinnla          | 0 to 2.3MHz for BW = 5MHz              |                                        |       | 1.3   |       | 4D                |

| Baseband Gain Ripple          | 0 to 4.6MHz for BW = 10MHz             |                                        |       | 1.3   |       | dB <sub>P-P</sub> |

| Baseband Croup Dolay Binnla   | 0 to 2.3MHz for BW = 5MHz              |                                        |       | 90    |       | no                |

| Baseband Group Delay Ripple   | 0 to 4.6MHz for BW = 10I               | MHz                                    |       | 50    |       | ns <sub>P-P</sub> |

| Baseband Filter Rejection for | At 3.3MHz                              |                                        |       | 7     |       | dB                |

| 5MHz RF Channel BW            | At > 21MHz                             |                                        |       | 85    |       | иь                |

| Baseband Filter Rejection for | At 6.7MHz                              |                                        |       | 7     |       | dB                |

| 10MHz RF Channel BW           | At > 41.6MHz                           |                                        |       | 85    |       | иь                |

| RSSI                          |                                        |                                        |       |       |       |                   |

| RSSI Minimum Output Voltage   | R <sub>LOAD</sub> ≥ 10kΩ               |                                        | 0.4   |       | V     |                   |

| RSSI Maximum Output Voltage   | R <sub>LOAD</sub> ≥ 10kΩ               |                                        | 2.2   |       | V     |                   |

| RSSI Slope                    |                                        |                                        | 30    |       | mV/dB |                   |

| RSSI Output Settling Time     | To within 3dB of steady                | +32dB signal step                      |       | 200   |       | nc                |

| 1.001 Output Settling Time    | state                                  | -32dB signal step                      |       | 800   |       | ns                |

### **AC Electrical Characteristics—Tx MODE**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $T_A$  = +25°C,  $f_{RF}$  = 2.502GHz,  $f_{LO}$  = 2.5GHz;  $f_{REF}$  = 40MHz, ENABLE = TXENABLE =  $\overline{CS}$  = high, and RXENABLE = SCLK = DIN = low, with power matching for the differential RF pins using the *Typical Operating Circuit*. Lowpass filter is set to 10MHz RF channel BW, 90mV<sub>RMS</sub> sine and cosine signal (or 90mV<sub>RMS</sub> 64QAM 1024-FFT OFDMA FUSC I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter (differential DC-coupled).) (Note 1)

| PARAMETER                                                           | CONDITIONS                                                                                                       | MIN     | TYP | MAX | UNITS |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------|-----|-----|-------|

| TRANSMIT SECTION: Tx BASEB                                          | AND I/Q INPUTS TO RF OUTPUTS                                                                                     |         |     |     |       |

| RF Output Frequency Range                                           |                                                                                                                  | 2.3     |     | 2.7 | GHz   |

| Peak-to-Peak Gain Variation over RF Band                            | Output optimally matched over 200MHz RF BW                                                                       |         | 2.5 |     | dB    |

| Total Voltage Gain                                                  | Max gain; at unbalanced 50Ω balun output                                                                         |         | 12  |     | dB    |

| Maximum Output Power over<br>Frequency for Any Given 200MHz<br>Band | OFDM signal conforming to spectral emission mask and -36dB EVM after I/Q imbalance calibration by modem (Note 3) | 0       |     |     | dBm   |

| RF Output Return Loss                                               | Given 200MHz band in the 2.3GHz to 2.7GHz range, for which the matching has been optimized                       | 8       |     |     | dB    |

| RF Gain Control Range                                               |                                                                                                                  |         | 45  |     | dB    |

| Unwanted Sideband Suppression                                       | Without calibration by modem, and excludes modem I/Q imbalance; P <sub>OUT</sub> = 0dBm                          | odem 45 |     |     | dBc   |

|                                                                     | B1                                                                                                               |         | 1   |     |       |

|                                                                     | B2                                                                                                               |         | 2   |     | ]     |

| RF Gain-Control Binary Weights                                      | B3                                                                                                               |         | 4   |     | dB    |

| RF Gain-Control Billary Weights                                     | B4                                                                                                               |         | 8   |     | ] ub  |

|                                                                     | B5                                                                                                               |         | 16  |     | ]     |

|                                                                     | B6                                                                                                               |         | 16  |     |       |

| Carrier Leakage                                                     | Relative to 0dBm output power; without calibration by modem                                                      |         | -35 |     | dBc   |

| T- 1/0                                                              | Minimum differential resistance                                                                                  |         | 100 |     | kΩ    |

| Tx I/Q Input Impedance (R    C)                                     | Maximum differential capacitance                                                                                 |         | 0.5 |     | pF    |

| Baseband Frequency Response                                         | 0 to 2.3MHz                                                                                                      |         | 0.2 |     | J.D.  |

| for 5MHz RF Channel BW                                              | At > 25MHz                                                                                                       | 80      |     |     | dB    |

| Baseband Frequency Response                                         | 0 to 4.6MHz                                                                                                      |         | 0.2 |     | ٩D    |

| for 10MHz RF Channel BW                                             | At > 17MHz                                                                                                       |         | 80  |     | dB    |

| Paschand Croup Dalay Binnia                                         | 0 to 2.3MHz (BW = 5MHz)                                                                                          |         | 20  |     |       |

| Baseband Group Delay Ripple                                         | 0 to 4.6MHz (BW = 10MHz)                                                                                         | 12      |     |     | ns    |

# **AC Electrical Characteristics—Frequency Synthesis**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 120kHz,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                 | CONDITIONS                                                                                                                           | MIN | TYP                | MAX | UNITS             |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------------------|

| FREQUENCY SYNTHESIZER                                     |                                                                                                                                      |     |                    |     |                   |

| RF Channel Center Frequency                               |                                                                                                                                      | 2.3 |                    | 2.7 | GHz               |

| Channel Center Frequency<br>Programming Minimum Step Size |                                                                                                                                      |     | 20                 |     | Hz                |

| Charge-Pump Comparison Frequency                          |                                                                                                                                      | 11  | 40                 |     | MHz               |

| Reference Frequency Range                                 |                                                                                                                                      | 11  | 40                 | 80  | MHz               |

| Reference Frequency Input<br>Levels                       | AC-coupled to XTAL2 pin                                                                                                              | 800 |                    |     | mV <sub>P-P</sub> |

| Reference Frequency Input                                 | Resistance (XTAL2 pin)                                                                                                               |     | 10                 |     | kΩ                |

| Impedance (R    C)                                        | Capacitance (XTAL2 pin)                                                                                                              |     | 1                  |     | pF                |

| Programmable Reference Divider Values                     |                                                                                                                                      | 1   | 2                  | 4   |                   |

| Closed-Loop Integrated Phase Noise                        | Loop BW = 120kHz; integrate phase noise from 200Hz to 5MHz, charge-pump comparison frequency = 40MHz                                 |     | -39                |     | dBc               |

| Charge-Pump Output Current                                | On each differential side                                                                                                            |     | 1.6                |     | mA                |

|                                                           | f <sub>OFFSET</sub> = 0 to 1.8MHz                                                                                                    |     | -40                |     |                   |

| Close-In Spur Level                                       | f <sub>OFFSET</sub> = 1.8MHz to 7MHz                                                                                                 |     | -70                |     | dBc               |

|                                                           | f <sub>OFFSET</sub> > 7MHz                                                                                                           |     | -80                |     |                   |

| Reference Spur Level                                      |                                                                                                                                      |     | -85                |     | dBc               |

| Turnaround LO Frequency Error                             | Relative to steady state; measured 35µs after Tx-Rx or Rx-Tx switching instant, and 4µs after any receiver gain changes              |     | ±50                |     | Hz                |

| Temperature Range over Which VCO Maintains Lock           | Relative to the ambient temperature T <sub>A</sub> , as long as the VCO lock temperature range is within operating temperature range |     | T <sub>A</sub> ±40 |     | °C                |

| Reference Output Clock Divider Values                     |                                                                                                                                      | 1   |                    | 2   |                   |

| Output Clock Drive Level                                  | 20MHz output, 1x drive setting                                                                                                       |     | 1.5                |     | V <sub>P-P</sub>  |

| Output Clock Minimum Load                                 | Resistance                                                                                                                           |     | 10                 |     | kΩ                |

| Impedance (R    C)                                        | Capacitance                                                                                                                          |     | 2                  |     | pF                |

### **AC Electrical Characteristics—Miscellaneous Blocks**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | CONDITION                                                | S                                                         | MIN T           | YP MAX | UNITS    |

|-----------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|-----------------|--------|----------|

| PA BIAS DAC: CURRENT MOD                | )E                                                       |                                                           | •               |        | <u>'</u> |

| Numbers of Bits                         |                                                          |                                                           |                 | Bits   |          |

| Minimum Output Sink Current             | D5:D0 = 000000 in A4:A0 = 11100                          |                                                           |                 | 0      | μA       |

| Maximum Output Sink Current             | D5:D0 = 111111 in A4:A0 = 11100                          |                                                           | 3               | 10     | μA       |

| Compliance Voltage Range                |                                                          |                                                           | 0.8             | 2.0    | V        |

| Turn-On Time                            | Excludes programmable delay of 0 f of 0.5µs              | Excludes programmable delay of 0 to 7μs in steps of 0.5μs |                 |        | ns       |

| DNL                                     |                                                          |                                                           |                 | 1      | LSB      |

| PA BIAS DAC: VOLTAGE MOD                | E                                                        |                                                           |                 |        |          |

| Output High Level                       | 10mA source current                                      |                                                           | V <sub>CC</sub> | V      |          |

| Output Low Level                        | 10mA sink current                                        |                                                           | 0.1             |        | V        |

| Turn-On Time                            | Excludes programmable delay of 0 f of 0.5µs              | o 7µs in steps                                            | 200             |        | ns       |

| CRYSTAL OSCILLATOR                      | ·                                                        |                                                           |                 |        | <u>.</u> |

| On-Chip Tuning Capacitance              | Maximum capacitance, A4:A0 = 11000, D6:D0 = 1111111      |                                                           | 15.5            |        |          |

| Range                                   | Minimum capacitance, A4:A0 = 11000, D6:D0 = 0000000      |                                                           | 0.5             |        | pF       |

| On-Chip Tuning Capacitance<br>Step Size |                                                          |                                                           | 0.              | .12    | pF       |

| ON-CHIP TEMPERATURE SEN                 | SOR                                                      |                                                           |                 |        |          |

|                                         | Bood out at DOLIT pin through CDI                        | T <sub>A</sub> = +25°C                                    | 01              | 111    |          |

| Digital Output Code                     | Read-out at DOUT pin through SPI<br>A4:A0 = 00111. D4:D0 | T <sub>A</sub> = +85°C                                    | 11              | 101    |          |

|                                         | 74.70 - 00111, 04.00                                     | T <sub>A</sub> = -40°C                                    | 00              | 001    |          |

## **AC Electrical Characteristics—Timing**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 120kHz,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                              | SYMBOL | CONDITIONS                                                                           |                    | MIN | TYP | MAX | UNITS |  |  |

|----------------------------------------|--------|--------------------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|--|--|

| SYSTEM TIMING                          |        |                                                                                      |                    |     |     |     |       |  |  |

| Turnaround Time                        |        | Measured from Tx or Rx enable rising edge;                                           | Rx to Tx           |     | 2   |     |       |  |  |

|                                        |        | signal settling to within 0.5dB of steady state                                      | Tx to Rx, RXHP = 1 |     | 2   |     | μs    |  |  |

| Tx Turn-On Time<br>(from Standby Mode) |        | Measured from Tx enable rising edge; signal settling to within 0.5dB of steady state |                    |     | 2   |     | μs    |  |  |

### **AC Electrical Characteristics—Timing (continued)**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, SCLK = DIN = low, PLL loop bandwidth = 120kHz,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                                              | SYMBOL           | CONDITIONS                                                                           | MIN TYP               | MAX | UNITS |

|----------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|-----------------------|-----|-------|

| Tx Turn-Off Time<br>(to Standby Mode)                                                  |                  | From Tx enable falling edge                                                          | 0.1                   |     | μs    |

| Rx Turn-On Time<br>(from Standby Mode)                                                 |                  | Measured from Rx enable rising edge; signal settling to within 0.5dB of steady state | 2                     |     | μs    |

| Rx Turn-Off Time<br>(to Standby Mode)                                                  |                  | From Rx enable falling edge                                                          | 0.1                   |     | μs    |

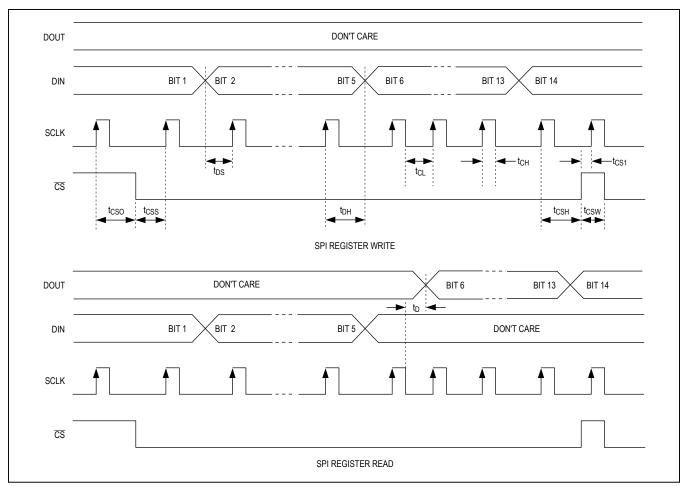

| 4-WIRE SERIAL-INTERFACE TIM                                                            | IING (See Fig    | gure 1)                                                                              |                       |     |       |

| SCLK Rising Edge to $\overline{\text{CS}}$ Falling Edge Wait Time                      | tcso             |                                                                                      | 6                     |     | ns    |

| Falling Edge of $\overline{\text{CS}}$ to Rising Edge of First SCLK Time               | t <sub>CSS</sub> |                                                                                      | 6                     |     | ns    |

| DIN to SCLK Setup Time                                                                 | t <sub>DS</sub>  |                                                                                      | 6                     |     | ns    |

| DIN to SCLK Hold Time                                                                  | t <sub>DH</sub>  |                                                                                      | 6                     |     | ns    |

| SCLK Pulse-Width High                                                                  | t <sub>CH</sub>  |                                                                                      | 6                     |     | ns    |

| SCLK Pulse-Width Low                                                                   | t <sub>CL</sub>  |                                                                                      | 6                     |     | ns    |

| Last Rising Edge of SCLK to<br>Rising Edge of CS or Clock to<br>Load Enable Setup Time | tcsн             |                                                                                      | 6                     |     | ns    |

| CS High Pulse Width                                                                    | t <sub>CSW</sub> |                                                                                      | 20                    |     | ns    |

| Time Between Rising Edge of CS and the Next Rising Edge of SCLK                        | t <sub>CS1</sub> |                                                                                      | 6                     |     | ns    |

| Clock Frequency                                                                        | f <sub>CLK</sub> |                                                                                      |                       | 45  | MHz   |

| Rise Time                                                                              | t <sub>R</sub>   |                                                                                      | f <sub>CLK</sub> / 10 | )   | ns    |

| Fall Time                                                                              | t <sub>F</sub>   |                                                                                      | f <sub>CLK</sub> / 10 | )   | ns    |

| SCLK Falling Edge to Valid DOUT                                                        | t <sub>D</sub>   |                                                                                      | 12.5                  |     | ns    |

Note 1: Min and max limits guaranteed by test above T<sub>A</sub> = +25°C and guaranteed by design and characterization at T<sub>A</sub> = -40°C. The power-on register settings are not production tested. Recommended register setting must be loaded after V<sub>CC</sub> is supplied.

Note 2: Two tones at +25MHz and +39MHz offset with -35dBm/tone. Measure IM3 at 1MHz.

Note 3: Gain adjusted over max gain and max gain - 3dB. Optimally matched over given 200MHz band.

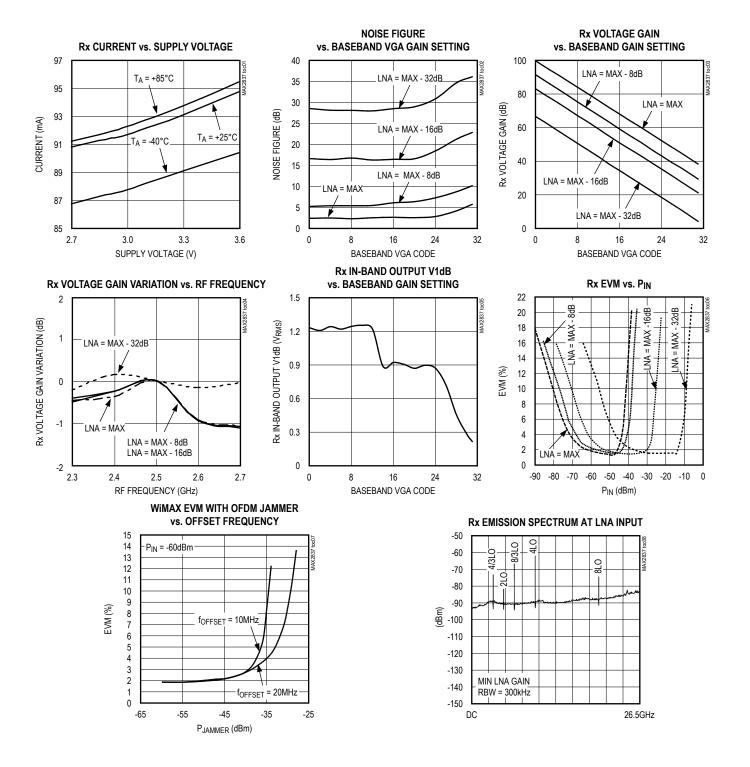

### **Typical Operating Characteristics**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz, 10MHz channel 16E UL/DL WiMax signal,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, RXHP = SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.)

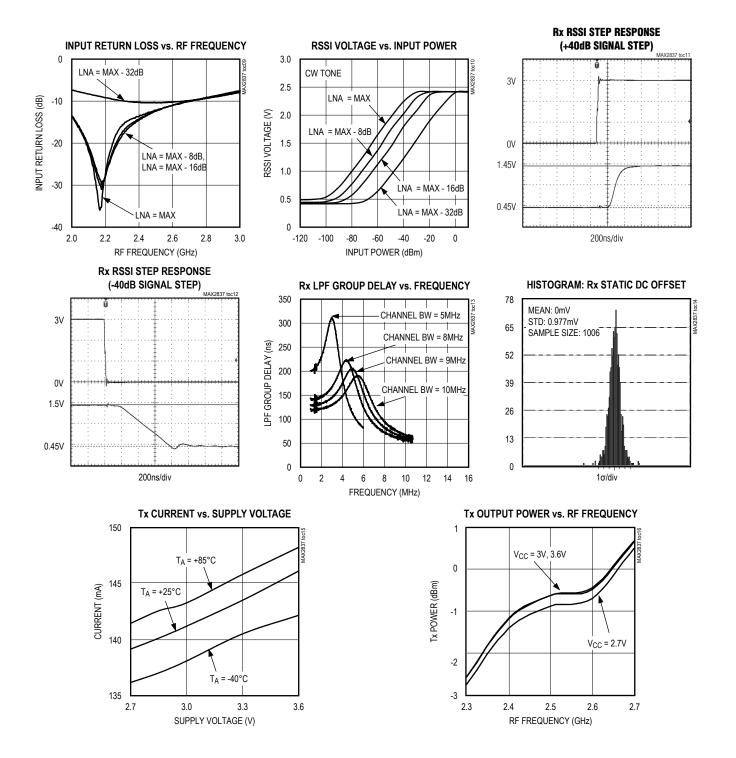

### **Typical Operating Characteristics (continued)**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz, 10MHz channel 16E UL/DL WiMax signal,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, RXHP = SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.)

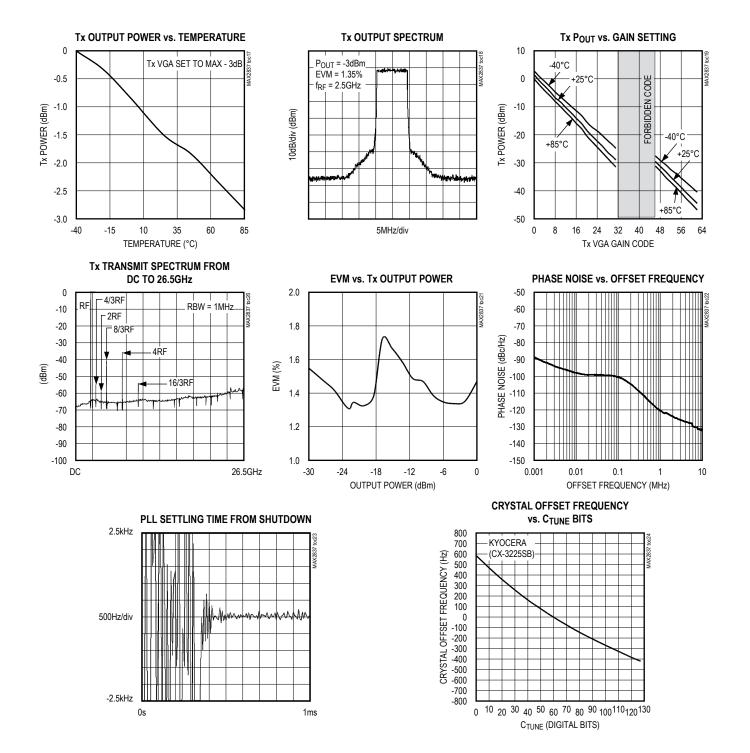

### **Typical Operating Characteristics (continued)**

(MAX2837 evaluation kit:  $V_{CC}$  = 2.8V,  $f_{LO}$  = 2.5GHz, 10MHz channel 16E UL/DL WiMax signal,  $f_{REF}$  = 40MHz, ENABLE =  $\overline{CS}$  = high, RXHP = SCLK = DIN = low,  $T_A$  = +25°C, unless otherwise noted.)

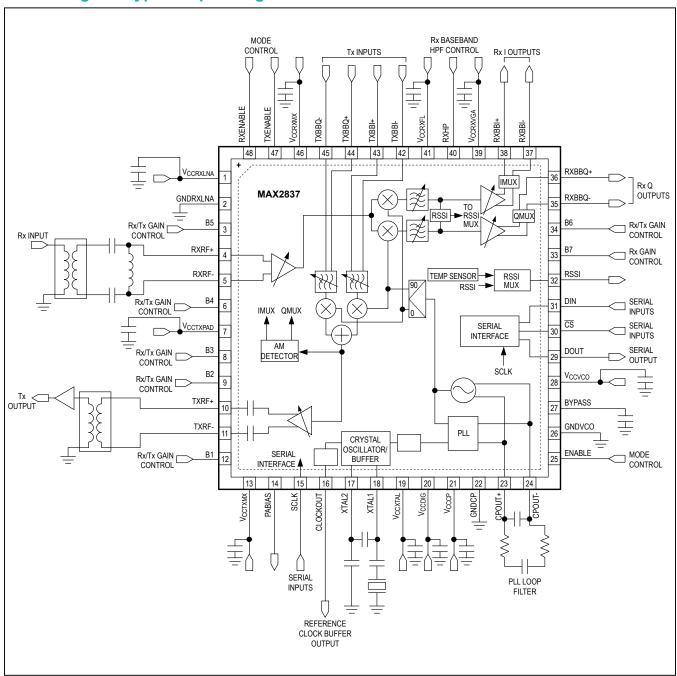

# **Block Diagram/Typical Operating Circuit**

# **Pin Description**

| PIN | NAME                  | FUNCTION                                                                                                                      |

|-----|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>CCRXLNA</sub>  | LNA Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                  |

| 2   | GNDRXLNA              | LNA Ground                                                                                                                    |

| 3   | B5                    | Receiver and Transmitter Gain-Control Logic Input Bit 5                                                                       |

| 4   | RXRF+                 | LNA Differential Inputs. Inputs are internally DC-coupled. An external shunt inductor and series                              |

| 5   | RXRF-                 | capacitors match the inputs to $100\Omega$ differential.                                                                      |

| 6   | B4                    | Receiver and Transmitter Gain-Control Logic Input Bit 4                                                                       |

| 7   | V <sub>CCTXPAD</sub>  | Supply Voltage for Power-Amplifier Driver. Bypass with a capacitor as close as possible to the pin.                           |

| 8   | В3                    | Receiver and Transmitter Gain-Control Logic Input Bit 3                                                                       |

| 9   | B2                    | Receiver and Transmitter Gain-Control Logic Input Bit 2                                                                       |

| 10  | TXRF+                 | Power-Amplifier Driver Differential Output. PA driver output is internally matched to a 100l differential.                    |

| 11  | TXRF-                 | The pins have internal DC-blocking capacitors.                                                                                |

| 12  | B1                    | Receiver and Transmitter Gain-Control Logic Input Bit 1                                                                       |

| 13  | V <sub>CCTXMX</sub>   | Transmitter Upconverter Supply Voltage. Bypass with a capacitor as close as possible to the pin.                              |

| 14  | PABIAS                | Transmit PA Bias DAC Output                                                                                                   |

| 15  | SCLK                  | Serial-Clock Logic Input of 4-Wire Serial Interface (See Figure 1)                                                            |

| 16  | CLOCKOUT              | Reference Clock Buffer Output                                                                                                 |

| 17  | XTAL2                 | Crystal or Reference Clock Input. AC-couple a crystal or a reference clock to this analog input.                              |

| 18  | XTAL1                 | Connection for Crystal-Oscillator Off-Chip Capacitors. When using an external reference clock input, leave XTAL1 unconnected. |

| 19  | V <sub>CCXTAL</sub>   | Crystal-Oscillator Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                   |

| 20  | V <sub>CCDIG</sub>    | Digital Circuit Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                      |

| 21  | V <sub>CCCP</sub>     | PLL Charge-Pump Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                      |

| 22  | GNDCP                 | Charge-Pump Circuit Ground                                                                                                    |

| 23  | CPOUT+                | Differential Charge-Pump Output. Connect the frequency synthesizer's loop filter between CPOUT+                               |

| 24  | CPOUT-                | and CPOUT (See the Typical Operating Circuit.)                                                                                |

| 25  | ENABLE                | Operation Mode Logic Input. See Table 1 for operating modes.                                                                  |

| 26  | GNDVCO                | VCO Ground                                                                                                                    |

| 27  | BYPASS                | On-Chip VCO Regulator Output Bypass. Bypass with a 1µF capacitor to GND. Do not connect other circuitry to this point.        |

| 28  | V <sub>CCVCO</sub>    | VCO Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                  |

| 29  | DOUT                  | Data Logic Output of 4-Wire Serial Interface (See Figure 1)                                                                   |

| 30  | CS                    | Chip-Select Logic Input of 4-Wire Serial Interface (See Figure 1)                                                             |

| 31  | DIN                   | Data Logic Input of 4-Wire Serial Interface (See Figure 1)                                                                    |

| 32  | RSSI                  | RSSI or Temperature Sensor Multiplexed Analog Output                                                                          |

| 33  | B7                    | Receiver Gain-Control Logic Input Bit 7                                                                                       |

| 34  | B6                    | Receiver and Transmitter Gain-Control Logic Input Bit 6                                                                       |

| 35  | RXBBQ-                | Receiver Baseband Q-Channel Differential Outputs. In Tx calibration mode, these pins are the                                  |

| 36  | RXBBQ+                | LO leakage and sideband detector outputs.                                                                                     |

| 37  | RXBBI-                | Receiver Baseband I-Channel Differential Outputs. In Tx calibration mode, these pins are the                                  |

| 38  | RXBBI+                | LO leakage and sideband detector outputs.                                                                                     |

| 39  | V <sub>CCRX</sub> VGA | Receiver VGA Supply Voltage                                                                                                   |

| 40  | RXHP                  | Receiver Baseband AC-Coupling Highpass Corner Frequency Control Logic Input                                                   |

|     |                       |                                                                                                                               |

### **Pin Description (continued)**

| PIN | NAME                | FUNCTION                                                                                                                                                                         |  |  |  |

|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 42  | TXBBI-              | Transmitter Received I Channel Differential Inputs                                                                                                                               |  |  |  |

| 43  | TXBBI+              | Transmitter Baseband I-Channel Differential Inputs                                                                                                                               |  |  |  |

| 44  | TXBBQ+              | Transmitter Deschand O Channel Differential Innuts                                                                                                                               |  |  |  |

| 45  | TXBBQ-              | Transmitter Baseband Q-Channel Differential Inputs                                                                                                                               |  |  |  |

| 46  | V <sub>CCRXMX</sub> | Receiver Downconverters Supply Voltage. Bypass with a capacitor as close as possible to the pin.                                                                                 |  |  |  |

| 47  | TXENABLE            | Tx Mode Control Logic Input. See Table 1 for operating modes.                                                                                                                    |  |  |  |

| 48  | RXENABLE            | Rx Mode Control Logic Input. See Table 1 for operating modes.                                                                                                                    |  |  |  |

| EP  | EP                  | Exposed Paddle. Connect to the ground plane with multiple vias for proper operation and heat dissipation. Do not share with any other pin grounds and bypass capacitors' ground. |  |  |  |

### **Table 1. Operating Mode Table**

| MODE              | LOGIC<br>PINS |          |          | REGISTER<br>SETTING |                | CIRCUIT<br>BLOCK STATES |                             |                     |                                |              |

|-------------------|---------------|----------|----------|---------------------|----------------|-------------------------|-----------------------------|---------------------|--------------------------------|--------------|

|                   | ENABLE        | RXENABLE | TXENABLE |                     | :D0<br>= 10000 | Rx<br>PATH              | Tx<br>PATH                  | PLL, VCO,<br>LO GEN | CALIBRATION SECTIONS ON        | CLOCK<br>OUT |

| Clock-Out         | 1             | 0        | 0        | 0                   | 0              | Off                     | Off                         | Off                 | None                           | On           |

| Shutdown          | 0             | 0        | 0        | 0                   | Х              | Off                     | Off                         | Off                 | None                           | Off          |

| Standby           | 1             | 0        | 0        | 0                   | 1              | Off*                    | Off*                        | On                  | None                           | On           |

| Rx                | 1             | 1        | 0        | 0                   | 1              | On                      | Off                         | On                  | None                           | On           |

| Tx                | 1             | 0        | 1        | 0                   | 1              | Off                     | On                          | On                  | None                           | On           |

| Rx<br>Calibration | 1             | 1        | 0        | 1                   | 1              | On<br>(Except<br>LNA)   | Off (Except Upconverters)   | On                  | Tx Baseband<br>Buffer          | On           |

| Tx<br>Calibration | 1             | 0        | 1        | 1                   | 1              | Off                     | On<br>(Except PA<br>Driver) | On                  | AM Detector, Rx<br>I/Q Buffers | On           |

<sup>\*</sup>Blocks of the transceiver can be selectively enabled through SPI.

### **Detailed Description**

### **Modes of Operation**

The modes of operation for the MAX2837 are clock-out, shutdown, transmit, receive, transmitter calibration, and receiver calibration. See Table 1 for a summary of the modes of operation. The logic input pins—ENABLE (pin 25), TXENABLE (pin 47), and RXENABLE (pin 48)—control the various modes. When the parts are active, various blocks can be shut down individually through SPI.

#### **Shutdown Mode**

The MAX2837 features a low-power shutdown mode. Current drain is the minimum possible with the supply voltages applied. In shutdown mode, all circuit blocks are powered down, except the 4-wire serial bus and its

internal programmable registers. If the supply voltage is applied, the registers are loaded and retained.

### **Standby Mode**

The standby mode is used to enable the frequency synthesizer block while the rest of the device is powered down. In this mode, PLL, VCO, and LO generator are on, so that Tx or Rx modes can be quickly enabled from this mode. These and other blocks can be selectively enabled in this mode.

### Receive (Rx) Mode

In receive mode, all Rx circuit blocks are powered on and active. Antenna signal is applied; RF is downconverted, filtered, and buffered at Rx BB I and Q outputs. The slow-charging Tx circuits are in a precharged "idle-off" state for fast Rx-to-Tx turnaround time.

Figure 1. 4-Wire SPI Serial-Interface Timing Diagram

### Transmit (Tx) Mode

In transmit mode, all Tx circuit blocks are powered on. The external PA is powered on after a programmable delay using the on-chip PA bias DAC. The slow-charging Rx circuits are in a precharged "idle-off" state for fast Tx-to-Rx turnaround time.

### **Clock-Out Only**

In clock-out mode, the entire transceiver is off except the divided reference clock output on the CLKOUT pin and the clock divider, which remains on.

# Temperature Sensor Readout Through DOUT Pin

To estimate chip temperature, on-chip temperature sensor is enabled by programming Address 9 D<1> = 1. The procedure is as follows:

- Enable temp-sensor by setting Address 9 D<1> = 1. Roughly 100μs to 1ms time is needed to let the temperature sensor output settle to within 5 to 1 degrees.

- 2) To trigger temperature sensor ADC, program Address 9 D<0> from "0" to "1". The ADC will acquire the 5-bit logic output in 2µs, temperature sensor needs to be ON (Address 9 D<1> = 1) to maintain the ADC logic output. Note that the ADC trigger should happen AFTER the temp sensor is enabled to get the correct result. Therefore, step 1 and step 2 of this procedure should be carried out on two separate SPI programming events separated by the temp sensor settling time.

- 3) Note that after the ADC latches its output and you desire to retake another temp sensor temperature reading value, the ADC has to be retriggered to reacquire a new temp sensor value (assuming the temp sensor is already enabled). To do so, program Address 9 D<0> from "1" to "0" then from "0" to "1". After the ADC latches it digital output in 2µs it shuts off.

- To read the 5-bit logic output through DOUT pin, apply 4-wire SPI readout programming sequence to Address 7.

### **VAS Operating Procedure**

After power-up, program Address 22 D<1> = 0 such that VAS frequency acquisition starts from VCO band 15, it reduces the worst-case acquisition time by half. VAS acquisition starts after Address 17 is programmed (i.e. rising edge of CSB), it takes the worst-case  $896\mu s$  to acquire lock.

Wireless LAN or MAN systems do not switch channel frequency often, die temperature may change quite a bit over time and makes PLL out of lock. To relock PLL as soon as possible, the user can program Address 22 D<1> = 1 after the first power-up frequency acquisition. VAS starts from the previous frequency subband and should relock PLL within 112µs.

### **VAS Readout**

The selected VCO subband, Vtune ADC output and VAS accomplished (VASA) signal can be read out through DOUT pin by programming Address 9 D<7:5> = 010 and corresponding Address 26 D<9:6>.

### **VCO Subband Selection Through SPI**

For very fast band selection operation, the user can characterize the mapping between VCO frequencies and corresponding subbands during factory calibration. After programming Address 22 D<0> = 0, the VCO subband can be selected by Address 23 D<4:0>.

# Programmable Registers and 4-Wire SPI Interface

The MAX2837 includes 32 programmable 16-bit registers. The most significant bit (MSB) is the read/write selection bit. The next 5 bits are register address. The 10 least significant bits (LSBs) are register data. Register data is loaded through the 4-wire SPI/MICROWIRE®-compatible serial interface. Data at DIN is shifted in MSB first and is framed by  $\overline{CS}$ . When  $\overline{CS}$  is low, the clock is active, and input data is shifted at the rising edge of the clock. During the read mode, register data selected by address bits is shifted out to DOUT at the falling edges of the clock. At the  $\overline{\text{CS}}$  rising edge, the 10-bit data bits are latched into the register selected by address bits. See Figure 1. The register values are preserved in shutdown mode as long as the power-supply voltage is maintained. However, every time the power-supply voltage is turned on, the registers are reset to the default values. Note that default register states are not guaranteed, and the user should always reprogram all registers after power-up.

MICROWIRE is a registered trademark of National Semiconductor Corp.

**Table 2. Recommended Register Settings**

| ADDRESS | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | HEX |

|---------|----|----|----|----|----|----|----|----|----|----|-----|

| 0       | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 150 |

| 1       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 002 |

| 2       | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 1F4 |

| 3       | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 1B9 |

| 4       | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 00A |

| 5       | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 080 |

| 6       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 006 |

| 7       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 000 |

| 8       | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 080 |

| 9       | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 018 |

| 10      | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 058 |

| 11      | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 016 |

| 12      | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 24F |

| 13      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 150 |

| 14      | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 1C5 |

| 15      | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 081 |

| 16      | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 01C |

| 17      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 155 |

| 18      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 155 |

| 19      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 153 |

| 20      | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 241 |

| 21      | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 02D |

| 22      | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1A9 |

| 23      | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 24F |

| 24      | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 180 |

| 25      | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 100 |

| 26      | 1  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 3CA |

| 27      | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 3E3 |

| 28      | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0C0 |

| 29      | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 3F0 |

| 30      | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 080 |

| 31      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 000 |

Table 3. Address 0, RXRF Register 1 (Default = 150<sub>HEX</sub>)

| DATA BITS | DEFAULT | DESCRIPTION                                                                                |

|-----------|---------|--------------------------------------------------------------------------------------------|

| D9        | 0       | Sets the center frequency of LNA output LC tank.  0 = Band 2.3~2.5GHz  1 = Band 2.5~2.7GHz |

| D8:D3     | 101010  | Set to recommended value.                                                                  |

| D2        | 0       | Enables RX quadrature generation, except for shut down mode.  1 = Enable  0 = Disabled     |

| D1        | 0       | Enables RX Mixer, except for shut down mode.  1 = Enable  0 = Disabled                     |

| D0        | 0       | Enables LNA, except for shut down mode.  1 = Enable  0 = Disabled                          |

# Table 4. Address 1, RXRF Register 2 (Default = 002<sub>HEX</sub>)

| DATA BITS | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                             |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D9:D5     | 00000   | RX LO IQ calibration SPI control. Active when Address 8 D<9> = 1. Serves as trim word of fuse links independent of Address 8 D<9>.  00000 = +4.0° phase error (default) (Q lags I signal by 94°).   01111 = 0.0° phase error.   11111 = -4.0° deg phase error (Q lags I signal by 86°). |

| D4:D2     | 000     | Adjusts the LNA gain by SPI. Active when Address 8 D<0> = 1.  000 = MAX gain (default)  100 = MAX-8dB  010 = MAX-16dB  110 = MAX-24dB  011 = MAX-32dB  111 = MAX-40dB                                                                                                                   |

| D1        | 1       | LNA output tank de_Q resistance tuning in 'Down' process.  0 = Nominal  1 = Increase ~2dB gain in down process (default)                                                                                                                                                                |

| D0        | 0       | LNA output LC tank center frequency tuning in 'Down' process.  0 = Nominal (default)  1 = Down process                                                                                                                                                                                  |

Table 5. Address 2, LPF Register 1 (Default = 1F4<sub>HEX</sub>)

| DATA BITS | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                        |

|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D9:D8     | 01      | Fine-tune the LPF cutoff frequency.  00 = -10%  01 = Nominal (default)  10 = Nominal  11 = +10%                                                                                                                                                                    |

| D7:D4     | 1111    | Sets the LPF RF Bandwidth.  0000 = 1.75MHz  0001 = 2.5MHz  0010 = 3.5MHz  0011 = 5.0MHz  0100 = 5.5MHz  0101 = 6.0MHz  0110 = 7.0MHz  0111 = 8.0MHz  1000 = 9.0MHz  1001 = 10.0MHz  1011 = 14.0MHz  1101 = 15.0MHz  1100 = 15.0MHz  1101 = 20.0MHz  1111 = 28.0MHz |

| D3:D2     | 01      | Sets the mode of the lowpass filter block. Active when Address 6 D<9> = 1.  00 = Rx Calibration  01 = Rx LPF (default)  10 = Tx LPF  11 = LPF Trim                                                                                                                 |