## **USB Host Adapter Emulators**

#### **General Description**

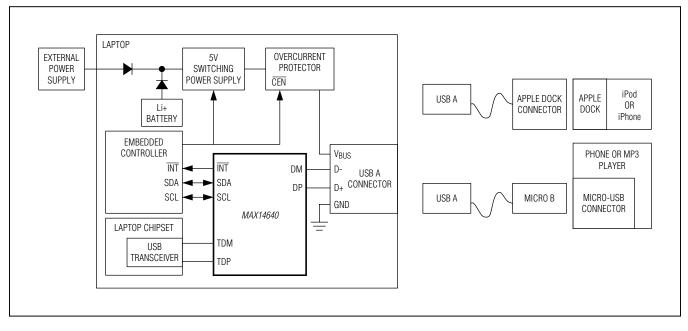

The MAX14640–MAX14644/MAX14651 are next-generation USB 2.0 host charger adapter emulators that combine USB Hi-Speed analog switches with a USB adapter emulator circuit.

The MAX14640/MAX14651 feature an I<sup>2</sup>C interface to fully configure the charging behavior with different address options. The MAX14641–MAX14644 are controlled by two GPIO inputs (CB1/CB0) and support USB data and automatic charger mode. In charging downstream port (CDP) pass-through mode, the devices emulate the CDP function while supporting normal USB traffic. The MAX14641/MAX14642/MAX14643 have a CEN output for an active-high CLS enable input, and the MAX14644 has a CEN output for an active-low CLS enable input to restart the peripheral connected to the USB host.

The MAX14640–MAX14644/MAX14651 feature 2A highcurrent autodetect mode. The MAX14641 features 1A high-current forced mode instead of regular DCP mode. The MAX14640/MAX14651 can be configured through I<sup>2</sup>C to support various dedicated charger modes such as DCP, Apple<sup>®</sup> 1A/2A forced, or Apple 1A/2A automatic mode.

All the devices support CDP and standard downstream port (SDP) charging while in the active state (S0) and support the dedicated charging port (DCP) charging while in the standby state (S3/S4/S5). All devices support low-speed remote wake-up by monitoring DM, and the MAX14642 also supports remote wake-up in sleep mode (S3).

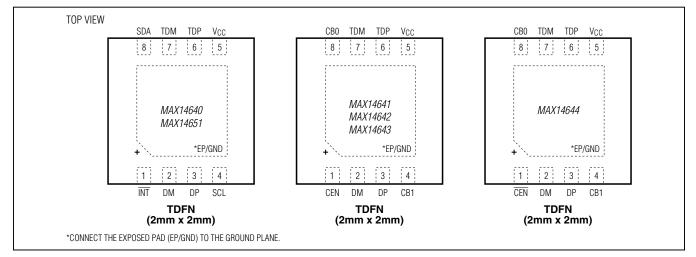

The MAX14640–MAX14644/MAX14651 are available in an 8-pin (2mm x 2mm) TDFN-EP package and are specified over the -40°C to +85°C extended temperature range.

#### **Benefits and Features**

- Improved Charger Interoperability

- USB (CDP) Emulation

- Smart CDP

- Foolproof CDP

- Meets New USB Battery Charging (BC) Revision

1.2 Specification

- Backward-Compatible with Previous USB BC Revisions

- Meets China YD/T1591-2009 Charging Specification

- Supports Standby-Mode Charging for Apple BC Revision 1.2 Compatible Devices

- Provide Greater Application Flexibility

- I<sup>2</sup>C Controls Multiple Modes (MAX14640/MAX14651)

- CB0 and CB1 Pins Control Multiple Automatic and Manual Charger States

- Enhance Performance with High Level of Integrated Features

Supports Remote Wakeup

- Low-Capacitance USB 2.0 Hi-Speed Switch to Change Charging Modes

- Automatic Current-Limit Switch Control

- ±15kV ESD Protection on DP/DM

- Minimize PCB Area

- 2mm x 2mm, 8-Pin TDFN Package

#### **Applications**

- Laptop/Desktop Computers

- USB Hubs

- Universal Chargers Including iPod®/iPhone®/iPad®

<u>Ordering Information</u> and <u>Typical Operating Circuit</u> appear at end of data sheet.

| Selector G | Suide |

|------------|-------|

|------------|-------|

| PART     | I/O MODE                | CEN POLARITY | REMOTE WAKE-UP IN AM | FORCED CHARGER MODE | <b>BIAS IN FM</b> |

|----------|-------------------------|--------------|----------------------|---------------------|-------------------|

| MAX14640 | I <sup>2</sup> C (0x35) | N/A          | Optional             | Yes                 | DP/DM short       |

| MAX14641 | GPIO                    | CEN          | No                   | No                  | Apple 1A          |

| MAX14642 | GPIO                    | CEN          | Yes                  | Yes                 | DP/DM short       |

| MAX14643 | GPIO                    | CEN          | No                   | Yes                 | DP/DM short       |

| MAX14644 | GPIO                    | CEN          | No                   | Yes                 | DP/DM short       |

| MAX14651 | I <sup>2</sup> C (0x15) | N/A          | Optional             | Yes                 | DP/DM short       |

Apple, iPad, iPod, and iPhone are registered trademarks of Apple, Inc.

### **USB Host Adapter Emulators**

#### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)                     |             |

|-------------------------------------------------------|-------------|

| V <sub>CC</sub> , TDP, TDM, DP, DM, SDA, SCL,         |             |

| CB0, CB1, CEN, CEN, INT                               | 0.3V to +6V |

| Continuous Current into Any Terminal                  | ±30mA       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |             |

| TDFN (derate 11.9mW/°C above +70°C)                   | 953.5mW     |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Package Thermal Characteristics (Note 1)

TDFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

#### **Electrical Characteristics**

$(V_{CC} = 3.0V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = 5.0V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                          | SYMBOL                            |                                                             | CONDITIONS                                  |      | ТҮР | MAX             | UNITS     |

|----------------------------------------------------|-----------------------------------|-------------------------------------------------------------|---------------------------------------------|------|-----|-----------------|-----------|

| POWER SUPPLY                                       |                                   | 1                                                           |                                             |      |     |                 |           |

|                                                    |                                   | CB0 = high                                                  |                                             | 3.0  |     | 5.5             | V         |

| V <sub>CC</sub> Supply Voltage                     | V <sub>CC</sub>                   | CB0 = low (No                                               | te 3)                                       | 4.75 |     | 5.25            | V         |

|                                                    |                                   |                                                             | CB1 = CB0 = low (AM2<br>mode)               |      |     | 200             |           |

|                                                    |                                   | MAX14641-<br>MAX14644                                       | CB1 = CB0 = high (CM<br>mode)               |      |     | 100             |           |

| V. Currely Current                                 |                                   |                                                             | CB1 = low, CB0 = high<br>(PM mode)          |      |     | 20              | - μΑ<br>- |

| V <sub>CC</sub> Supply Current                     | ICC                               |                                                             | MODE_SEL[2:0] = 000<br>(AM2 mode)           |      |     | 200             |           |

|                                                    |                                   | MAX14640/<br>MAX14651                                       | MODE_SEL[2:0] = 011<br>(CM mode)            |      |     | 100             |           |

|                                                    |                                   |                                                             | MODE_SEL[2:0] = 001<br>(PM mode)            |      |     | 20              |           |

| POR Delay                                          | t <sub>POR</sub>                  |                                                             | ·                                           |      | 50  |                 | ms        |

| ANALOG SWITCHES (DP, DM                            | , TDP, TDM)                       |                                                             |                                             |      |     |                 |           |

| Analog Signal Range                                | V <sub>DP</sub> , V <sub>DM</sub> | (Note 4)                                                    |                                             | 0    |     | V <sub>CC</sub> | V         |

| TDP/TDM On Resistance                              | R <sub>ON</sub>                   | $V_{IN} = 0V \text{ to } V_C$                               | $_{\rm C}$ , $I_{\rm IN}$ = 10mA            |      | 3.5 | 6.5             | Ω         |

| TDP/TDM On-Resistance<br>Matching Between Channels | ΔR <sub>ON</sub>                  | $V_{\rm CC} = 5.0V, I_{\rm IN}$                             | <sub>N</sub> = 10mA, V <sub>IN</sub> = 0.4V |      | 0.1 |                 | Ω         |

| TDP/TDM On-Resistance<br>Flatness                  | R <sub>FLAT</sub>                 | $V_{CC}$ = 5.0V, $I_{IN}$ = 10mA, $V_{IN}$ = 0V to $V_{CC}$ |                                             |      | 0.1 |                 | Ω         |

| DP/DM Short On-Resistance                          | R <sub>SHORT</sub>                | V <sub>DP</sub> = 1V, R <sub>L</sub> =                      | = 20k $\Omega$ on DM                        |      | 70  | 128             | Ω         |

# USB Host Adapter Emulators

### **Electrical Characteristics (continued)**

$(V_{CC} = 3.0V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = 5.0V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                       | SYMBOL                                                                                                         | CONDITIONS                                                                            | MIN   | ТҮР   | МАХ   | UNITS |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Off Leakage Current                             | Dff Leakage Current $I_{COM(OFF)}$ $V_{CC} = 3.6V, V_{DP} = V_{DM} = V_{TDP} = V_{TDM} = 3.3V \text{ to } 0.3$ |                                                                                       | -1    | 1.5nA | +1    | μA    |

| On Leakage Current                              | I <sub>COM(ON)</sub>                                                                                           | $V_{CC} = 3.6V, V_{DP} = V_{DM} = 0.3V$ to 3.3V                                       | -1    | 90nA  | +1    | μA    |

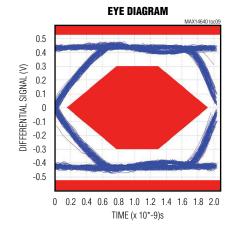

| DYNAMIC PERFORMANCE                             |                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                                 |       |       |       |       |

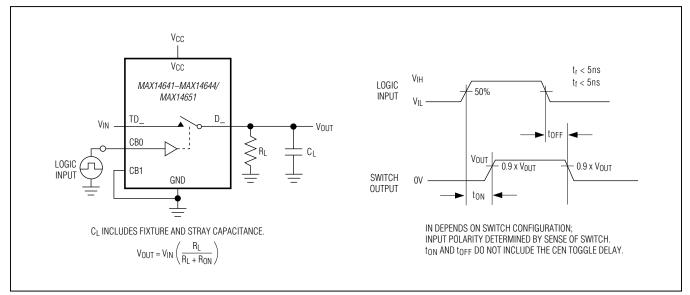

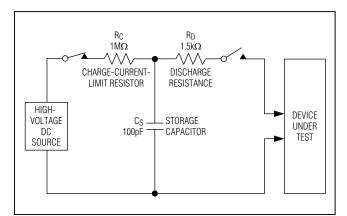

| Turn-On Time                                    | t <sub>ON</sub>                                                                                                | $V_{TDP}$ or $V_{TDM}$ = 1.5V, $R_L$ = 300 $\Omega$ , $C_L$ = 35pF, Figure 1 (Note 4) |       | 20    |       | μs    |

| Turn-Off Time                                   | tOFF                                                                                                           | $V_{TDP}$ or $V_{TDM}$ = 1.5V, $R_L$ = 300 $\Omega$ , $C_L$ = 35pF, Figure 1 (Note 4) |       | 1     |       | μs    |

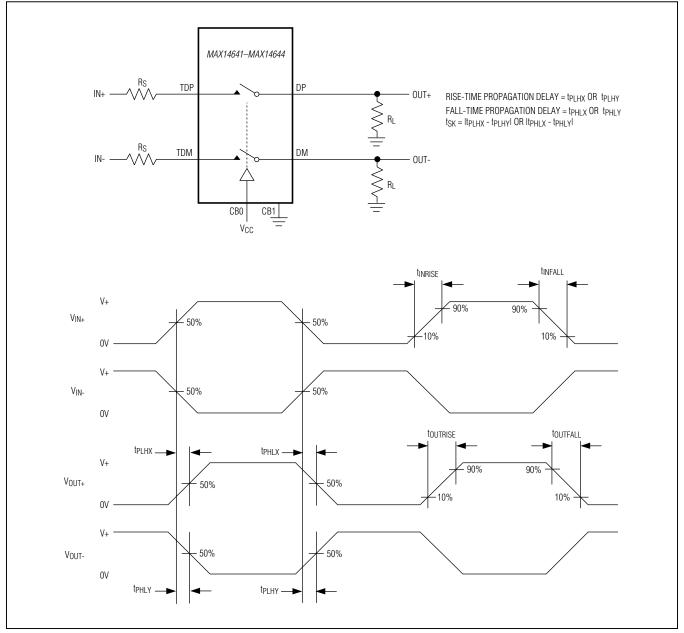

| TDP/TDM Propagation Delay                       | t <sub>PHL</sub> , t <sub>PLH</sub>                                                                            | $R_L = R_S = 50\Omega$ , DP and DM connected to TDP and TDM, Figure 2                 |       | 60    |       | ps    |

| DP/DM Output Skew                               | <sup>t</sup> SKEW                                                                                              | $R_L = R_S = 50\Omega$ , DP and DM connected to TDP and TDM, Figure 2                 |       | 40    |       | ps    |

| DP/DM On-Capacitance<br>(Connected to TDP, TDM) | C <sub>OFF</sub>                                                                                               | $f = 240MHz$ , $V_{BIAS} = 0V$ , $V_{IN} = 500mV_{P-P}$                               |       | 5     |       | pF    |

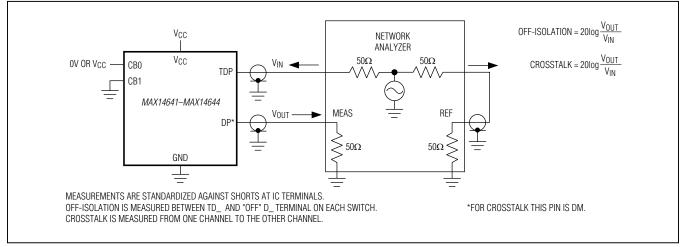

| Bandwidth                                       | BW                                                                                                             | $R_L = R_S = 50\Omega$ , Figure 3                                                     |       | 1000  |       | MHz   |

| Off-Isolation                                   | V <sub>ISO</sub>                                                                                               | $V_{IN} = 0$ dBm, $R_L = R_S = 50\Omega$ , f = 250MHz, Figure 3                       |       | -20   |       | dB    |

| Crosstalk                                       | V <sub>CT</sub>                                                                                                | $V_{IN}$ = 0dBm, $R_L$ = $R_S$ = 50 $\Omega$ , f = 250MHz, Figure 3                   |       | -25   |       | dB    |

| DCP INTERNAL RESISTORS                          | <b>I</b>                                                                                                       |                                                                                       |       |       |       |       |

| DP/DM Short Pulldown                            | R <sub>PD</sub>                                                                                                |                                                                                       | 320   | 500   | 700   | kΩ    |

| RP1/RP2 Ratio                                   | RT <sub>RP</sub>                                                                                               |                                                                                       | 1.485 | 1.5   | 1.515 |       |

| RP1 + RP2 Resistance                            | R <sub>RP</sub>                                                                                                |                                                                                       | 92    | 125   | 158.5 | kΩ    |

| RM1/RM2 Ratio                                   | RT <sub>RM</sub>                                                                                               |                                                                                       | 0.844 | 0.85  | 0.864 |       |

| RM1 + RM2 Resistance                            | R <sub>RM</sub>                                                                                                |                                                                                       | 68    | 93    | 118   | kΩ    |

| RSS1/RSS2 Ratio                                 | RT <sub>RSS</sub>                                                                                              |                                                                                       | 2.9   | 3     | 3.1   |       |

| RSS1 + RSS2 Resistance                          | R <sub>RSS</sub>                                                                                               |                                                                                       | 30    | 40    | 60    | kΩ    |

| CDP INTERNAL RESISTORS                          |                                                                                                                |                                                                                       |       |       |       |       |

| DP Pulldown Resistor                            | R <sub>DP_CDP</sub>                                                                                            | CDP mode                                                                              | 14.25 | 19.53 | 24.80 | kΩ    |

| DM Pulldown Resistor                            | R <sub>DM_CDP</sub>                                                                                            | CDP mode                                                                              | 14.25 | 19.53 | 24.8  | kΩ    |

| CDP HIGH-SPEED COMPARA                          | TORS                                                                                                           |                                                                                       |       |       |       |       |

| Threshold Voltage                               | V <sub>TH_CDP</sub>                                                                                            |                                                                                       | 100   | 161   | 205   | mV    |

| CDP LOW-SPEED COMPARA                           | TORS                                                                                                           |                                                                                       |       |       |       |       |

| V <sub>DM SRC</sub> Voltage                     | V <sub>DM SRC</sub>                                                                                            | $I_{LOAD} = 0$ to 200µA                                                               | 0.5   |       | 0.7   | V     |

### **USB Host Adapter Emulators**

### **Electrical Characteristics (continued)**

$(V_{CC} = 3.0V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = 5.0V \text{ and } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                          | SYMBOL               | COND                                                                                               | ITIONS                                         | MIN                   | ТҮР | MAX | UNITS |

|----------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------|-----|-----|-------|

| V <sub>DP_REF</sub> Voltage                        | V <sub>DP_REF</sub>  |                                                                                                    |                                                | 0.25                  |     | 0.4 | V     |

| V <sub>LGC</sub> Voltage                           | V <sub>LGC</sub>     |                                                                                                    |                                                | 0.8                   |     | 2.0 | V     |

| I <sub>DP_SINK</sub> Current                       | I <sub>DP_SINK</sub> | $V_{DP} = 0.15V \text{ to } 3.6V$                                                                  |                                                | 50                    |     | 150 | μA    |

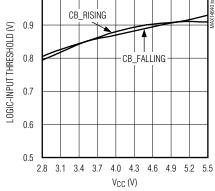

| LOGIC INPUTS (CB0, CB1, SDA,                       | SCL)                 |                                                                                                    |                                                | ·                     |     |     |       |

| Input Logic High Voltage                           | VIH                  |                                                                                                    |                                                | 1.4                   |     |     | V     |

| Input Logic Low Voltage                            | VIL                  |                                                                                                    |                                                |                       |     | 0.4 | V     |

| Input Leakage Current                              | I <sub>IN</sub>      | $\begin{array}{c} 0V \leq V_{IN} \leq V_{IL} \text{ or } V_{IH} \leq \\ V_{CC} = 5.5V \end{array}$ | $\leq V_{IN} \leq V_{CC},$                     | -1                    |     | +1  | μA    |

| CB0/CB1 Debounce Time                              | tDEB_CB_             |                                                                                                    |                                                |                       | 250 |     | μs    |

| OPEN-DRAIN LOGIC OUTPUTS                           | (SDA, ĪNT, C         | EN, CEN)                                                                                           |                                                | ·                     |     |     |       |

| ĪNT, SDA, CEN Output Low<br>Voltage                | V <sub>OL</sub>      | Output asserted, ISIN                                                                              | <sub>K</sub> = 4mA                             |                       |     | 0.4 | V     |

| INT, SDA, CEN Output Leakage<br>Current            | IOH                  | Output not asserted,                                                                               | Output not asserted, $V_{CC} = V_{OUT} = 5.5V$ |                       |     | 1   | μA    |

| CEN, INT, Output High Voltage                      | V <sub>OH</sub>      | Output asserted, I <sub>SOURCE</sub> = 4mA                                                         |                                                | V <sub>CC</sub> - 0.4 | Ļ   |     | V     |

| CEN, INT, Output Leakage Current                   | I <sub>OL</sub>      | Output not asserted, V                                                                             | $CC = 5.5V, V\overline{CEN} = 0V$              |                       |     | 1   | μA    |

| V <sub>BUS</sub> Toggle Time Accuracy              | t <sub>VBT</sub>     |                                                                                                    |                                                |                       | ±10 |     | %     |

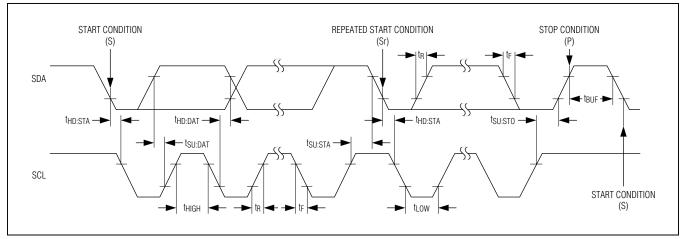

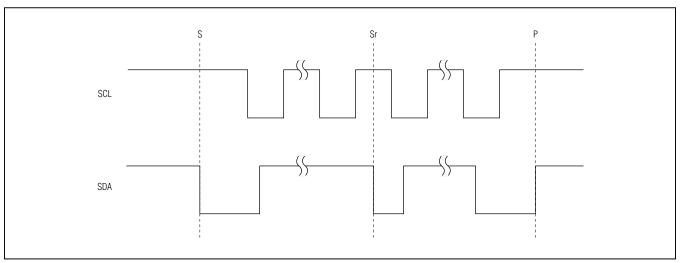

| I <sup>2</sup> C TIMING CHARACTERISTICS            | (SEE FIGUR           | E 4)                                                                                               |                                                |                       |     |     |       |

| I <sup>2</sup> C Maximum Clock Frequency           | fSCL                 |                                                                                                    |                                                |                       |     | 400 | kHz   |

| Bus Free Time Between STOP<br>and START Conditions | t <sub>BUF</sub>     |                                                                                                    |                                                | 1.3                   |     |     | μs    |

| START Condition Setup Time                         | t <sub>SU:STA</sub>  |                                                                                                    |                                                | 0.6                   |     |     | μs    |

| Repeated START Condition<br>Setup Time             | t <sub>SU:STA</sub>  | 70% of SCL to 70% of                                                                               | f SDA                                          | 0.6                   |     |     | μs    |

| START Condition Hold Time                          | thd:sta              | 30% of SDA to 70% o                                                                                | f SCL                                          | 0.6                   |     |     | μs    |

| STOP Condition Setup Time                          | tsu:sto              | 70% of SCL to 30% of                                                                               | f SDA                                          | 0.6                   |     |     | μs    |

| Clock Low Period                                   | t <sub>LOW</sub>     | 30% to 30%                                                                                         |                                                | 1.3                   |     |     | μs    |

| Clock High Period                                  | thigh                | 70% to 70%                                                                                         |                                                | 0.6                   |     |     | μs    |

| Data Valid to SCL Rise Time                        | t <sub>SU:DAT</sub>  | Write setup time 1                                                                                 |                                                | 100                   |     |     | ns    |

| Data Hold Time to SCL Fall                         | thd:dat              | Write hold time                                                                                    |                                                |                       | 100 |     | ns    |

| PROTECTION SPECIFICATIONS                          |                      |                                                                                                    |                                                |                       |     |     |       |

| ESD Protection                                     | V <sub>ESD</sub>     | Human Body Model                                                                                   | DP and DM pins                                 |                       | ±15 |     | kV    |

|                                                    | VESD                 |                                                                                                    | All other pins                                 |                       | ±2  |     |       |

Note 2: All units are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

**Note 3:** The MAX1464\_ is operational from 3.0V to 5.5V. However, in order for the valid Apple resistor-divider network to function,  $V_{CC}$  must stay within the 4.75V to 5.25V range.

**Note 4:** Guaranteed by design, not production tested.

Note 5: Guaranteed by design.

# USB Host Adapter Emulators

### **Test Circuits/Timing Diagrams**

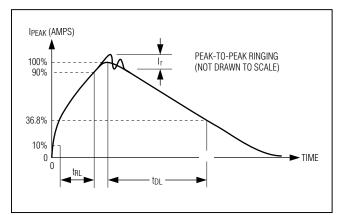

Figure 1. Switching Time

# USB Host Adapter Emulators

## Test Circuits/Timing Diagrams (continued)

Figure 2. Propagation Delay and Output Skew

## USB Host Adapter Emulators

### **Test Circuits/Timing Diagrams (continued)**

Figure 3. Bandwidth, Off-Isolation, and Crosstalk

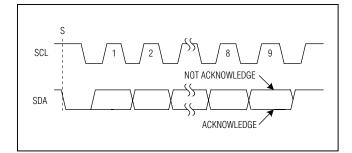

Figure 4. I<sup>2</sup>C Timing Diagram. Note that  $t_R$  and  $t_F$  are per the I<sup>2</sup>C fast-mode specification.

## **USB Host Adapter Emulators**

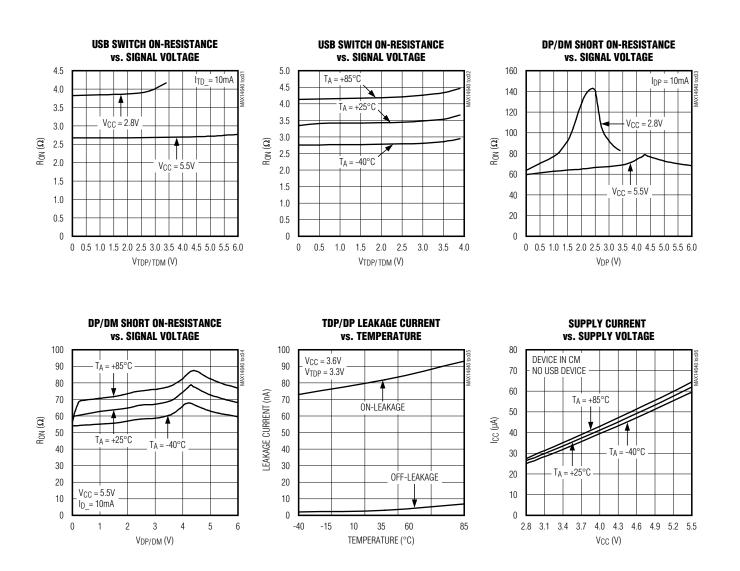

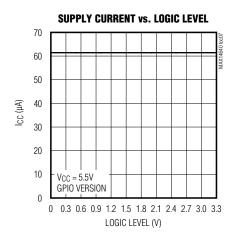

## **Typical Operating Characteristics**

(V<sub>CC</sub> = +5V,  $T_A$  = +25°C, unless otherwise noted.)

## **USB Host Adapter Emulators**

### **Typical Operating Characteristics**

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

1.0

## **USB Host Adapter Emulators**

# **Pin Configurations**

### **Pin Description**

|                       | PIN                                |          |                 |                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------------|------------------------------------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX14640/<br>MAX14651 | MAX14641/<br>MAX14642/<br>MAX14643 | MAX14644 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                          |  |

| 1                     | _                                  |          | ĪNT             | Open-Drain Interrupt Output. INT asserts low when interrupt occurs.                                                                                                                                                                                                                                                               |  |

| _                     | 1                                  | _        | CEN             | nMOS Open-Drain Output. Pull up CEN to V <sub>CC</sub> by 10k $\Omega$ . CEN high enables the current-limit switch and V <sub>BUS</sub> ON, and nMOS ON makes CEN low and the current-limit switch OFF. When CB_ transitions from low to high or high to low, CEN is low for 1s (typ).                                            |  |

| _                     | _                                  | 1        | CEN             | pMOS Open-Drain Output. Pull down $\overline{CEN}$ to GND by 10k $\Omega$ . $\overline{CEN}$ low enables the current-limit switch and V <sub>BUS</sub> ON, and pMOS ON makes $\overline{CEN}$ high and the current-limit switch OFF. When CB_ transitions from low to high or high to low, $\overline{CEN}$ is high for 1s (typ). |  |

| 2                     | 2                                  | 2        | DM              | USB Connector D- Connection                                                                                                                                                                                                                                                                                                       |  |

| 3                     | 3                                  | 3        | DP              | USB Connector D+ Connection                                                                                                                                                                                                                                                                                                       |  |

| 4                     |                                    |          | SCL             | I <sup>2</sup> C Serial-Clock Input                                                                                                                                                                                                                                                                                               |  |

|                       | 4                                  | 4        | CB1             | Switch Control Input Bit 1. See the Switch Control Input Truth tables (Tables 2, 3, and 4).                                                                                                                                                                                                                                       |  |

| 5                     | 5                                  | 5        | V <sub>CC</sub> | Power-Supply Input. Bypass $V_{CC}$ to GND with a 0.1 $\mu F$ ceramic capacitor as close as possible to the device.                                                                                                                                                                                                               |  |

| 6                     | 6                                  | 6        | TDP             | Host USB Transceiver D+ Connection                                                                                                                                                                                                                                                                                                |  |

| 7                     | 7                                  | 7        | TDM             | Host USB Transceiver D- Connection                                                                                                                                                                                                                                                                                                |  |

| 8                     | _                                  | _        | SDA             | I <sup>2</sup> C Serial-Data Input/Output                                                                                                                                                                                                                                                                                         |  |

| _                     | 8                                  | 8        | CB0             | Switch Control Input Bit 0. See the Switch Control Input Truth tables (Tables 2, 3, and 4).                                                                                                                                                                                                                                       |  |

| _                     | _                                  |          | EP/<br>GND      | Exposed Pad and Ground. The exposed pad is the ground connection for the device. Connect EP/GND to the ground plane.                                                                                                                                                                                                              |  |

# USB Host Adapter Emulators

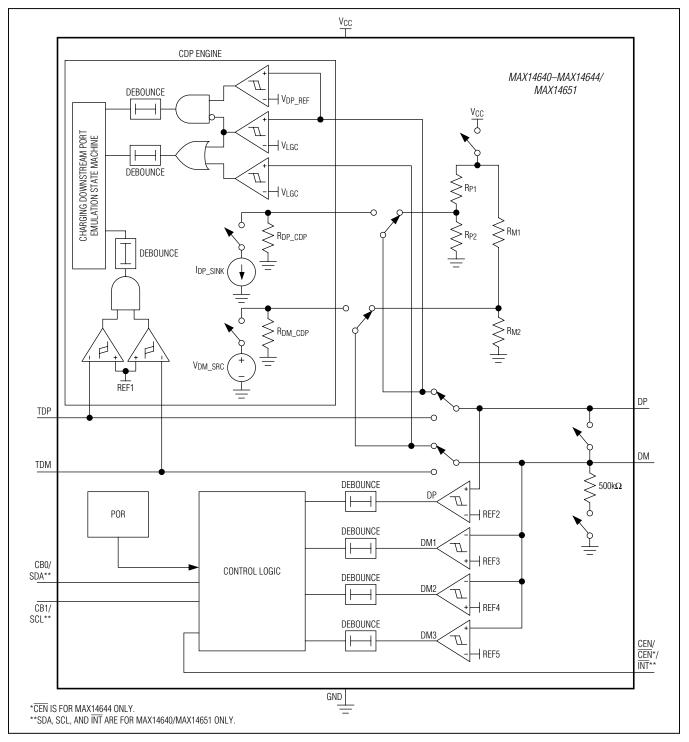

### **Functional Diagram**

#### **Detailed Description**

The MAX14640–MAX14644/MAX14651 adapter emulator devices have high-speed USB analog switches that support USB hosts by identifying the USB port as a charger when the USB host is in a low-power mode and cannot enumerate USB devices. The devices feature low 4pF (typ) on-capacitance and low 4 $\Omega$  (typ) on-resistance when the USB switches are connected. DP and DM are capable of handling signals between 0V and 5.5V over the entire 3.0V–5.5V supply range.

The MAX14640/MAX14651 are controlled by an I<sup>2</sup>C interface, while the MAX14641–MAX14644 are controlled by the CB0 and CB1 logic inputs. The I<sup>2</sup>C interface allows further customization over which mode the MAX14640/MAX14651 operate in and can be used to read back connection information.

Improvements over the MAX14600 USB detector family include support for some smartphones that do not connect after applying 0.6V in charging downstream port (CDP) mode. The devices also support high-current charging of Apple devices while in sleep mode.

#### **Resistor-Dividers**

The MAX14640–MAX14644/MAX14651 feature internal resistor-divider networks on the data lines to provide support for Apple devices. The resistor-divider is disconnected while not in use to minimize the supply current. The resistor-dividers are not connected in pass-through mode. Table 1 summarizes the resistor values connected to DP/DM in different charging modes.

#### **Switch Control**

#### **Digital Controls**

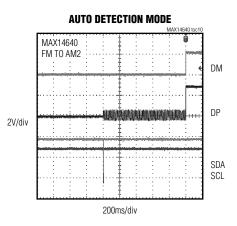

The MAX14641–MAX14644 feature two digital select inputs, CB0 and CB1, for mode selection. <u>Table 2</u>, <u>Table 3</u>, and <u>Table 4</u> show how the CB1/CB0 inputs can be used to enter autodetection charger mode (AM\_), pass-through mode (PM), forced charger mode (FM and AP\_), and pass-through mode with CDP emulation (CM).

In CDP emulation mode, the peripheral device with CDP detection capability draws charging current up to 1.5A immediately without USB enumeration.

#### Table 1. DP/DM Resistor-Dividers

| CHARGING MODE | DP PULLUP (kΩ) | DP PULLDOWN (k $\Omega$ ) | DM PULLUP (k $\Omega$ ) | DM PULLDOWN (kΩ) |

|---------------|----------------|---------------------------|-------------------------|------------------|

| AM1           | 75             | 49.9                      | 43.2                    | 49.9             |

| AM2           | 43.2           | 49.9                      | 75                      | 49.9             |

#### Table 2. Digital Input State Table for the MAX14641

| CB1 | CB0 | CHARGER/USB | MODE | STATUS                                                                                                      |

|-----|-----|-------------|------|-------------------------------------------------------------------------------------------------------------|

| 0   | 0   | CHARGER     | AM2  | 2A Autodetection Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                  |

| 1   | 0   | CHARGER     | AP1  | Forced 1A Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                         |

| 0   | 1   | USB         | PM   | USB Pass-Through Mode. DP/DM are connected to TDP/TDM.                                                      |

| 1   | 1   | USB         | СМ   | USB Pass-Through Mode with CDP Emulation. Auto connects DP/DM to TDM/TDM depending on CDP detection status. |

#### Table 3. Digital Input State Table for the MAX14642

| CB1 | CB0 | CHARGER/USB | MODE | STATUS                                                                                                      |

|-----|-----|-------------|------|-------------------------------------------------------------------------------------------------------------|

| Х   | 0   | CHARGER     | AM2  | 2A Autodetection Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                  |

| 0   | 1   | USB         | PM   | USB Pass-Through Mode. DP/DM are connected to TDP/TDM.                                                      |

| 1   | 1   | USB         | СМ   | USB Pass-Through Mode with CDP Emulation. Auto connects DP/DM to TDM/TDM depending on CDP detection status. |

X = Don't care.

#### Table 4. Digital Input State Table for the MAX14643/MAX14644

| CB1 | CB0 | CHARGER/USB | MODE | STATUS                                                                                                      |

|-----|-----|-------------|------|-------------------------------------------------------------------------------------------------------------|

| 0   | 0   | CHARGER     | AM2  | 2A Autodetection Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                  |

| 1   | 0   | CHARGER     | FM   | Forced Dedicated Charger Mode. DP and DM are shorted.                                                       |

| 0   | 1   | USB         | PM   | USB Pass-Through Mode. DP/DM are connected to TDP/TDM.                                                      |

| 1   | 1   | USB         | СМ   | USB Pass-Through Mode with CDP Emulation. Auto connects DP/DM to TDM/TDM depending on CDP detection status. |

#### Table 5. Digital Input State Table for the MAX14640/MAX14651

| МО  | DE_S | EL  |             | MODE | 074710                                                                                                      |

|-----|------|-----|-------------|------|-------------------------------------------------------------------------------------------------------------|

| [2] | [1]  | [0] | CHARGER/USB | MODE | STATUS                                                                                                      |

| 0   | 0    | 0   | CHARGER     | AM2  | 2A Autodetection Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                  |

| 0   | 0    | 1   | USB         | PM   | USB Pass-Through Mode. DP/DM are connected to TDP/TDM.                                                      |

| 0   | 1    | 0   | CHARGER     | FM   | Forced Dedicated Charger Mode. DP and DM are shorted.                                                       |

| 0   | 1    | 1   | USB         | СМ   | USB Pass-Through Mode with CDP Emulation. Auto connects DP/DM to TDM/TDM depending on CDP detection status. |

| 1   | 0    | 0   | CHARGER     | AM1  | 1A Autodetection Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                  |

| 1   | 0    | 1   | CHARGER     | AP1  | Forced 1A Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                         |

| 1   | 1    | 0   | CHARGER     | AP2  | Forced 2A Charger Mode for Apple Devices. Resistor-dividers are connected to DP/DM.                         |

| 1   | 1    | 1   | CHARGER     | SS   | Forced 2A Charger Mode for Samsung Galaxy Tablet                                                            |

#### I<sup>2</sup>C Controls

The MAX14640/MAX14651 mode is controlled by the MODE\_SEL[2:0] bits. <u>Table 5</u> shows how these bits control the device. In addition to being configurable in all modes that the MAX14641–MAX14644 can enter, the MAX14640/MAX14651 can be configured to be compatible with the Apple and Samsung<sup>®</sup> Galaxy (SS mode) devices.

#### Legacy D+/D- Detect

The MAX14640–MAX14644/MAX14651 support charging devices that use a D+/D- short to indicate it is ready for charging. This is done by monitoring the voltage at both the DP and DM terminals and triggering when they are both higher than their comparator thresholds.

Samsung is a registered trademark of Samsung Electronics, Co., Ltd.

### **USB Host Adapter Emulators**

#### **Auto Peripheral Reset**

The MAX14641–MAX14644 feature an auto currentlimit switch control output. This feature resets the peripheral connected to  $V_{BUS}$  in the event the USB host switches to or from standby mode. CEN or CEN are pulsed for 1s<sup>\*</sup> (typ) on the rising or falling edge of CB0 or CB1 (Figure 5 and Figure 6).

\*Note: 2s (typ) for the MAX14644ETA+TCNE.

#### **Pass-Through Modes**

If the MAX14640–MAX14644/MAX14651 are configured in pass-through mode (PM), then TDP/TDM are always connected to DP/DM and no resistor-dividers or power sources are applied to DP/DM.

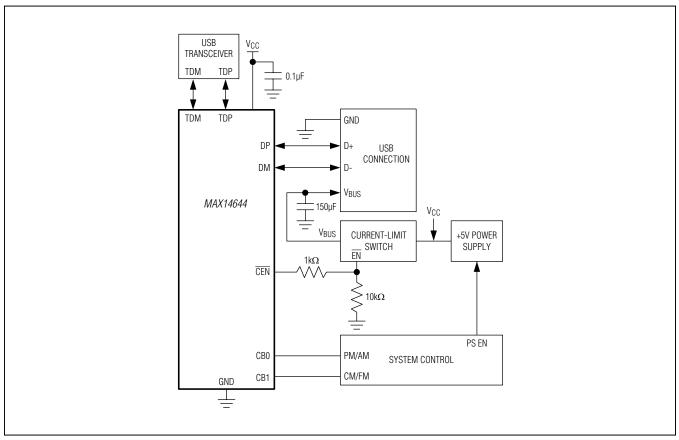

Figure 5. MAX14644 Peripheral Reset Applications Diagram

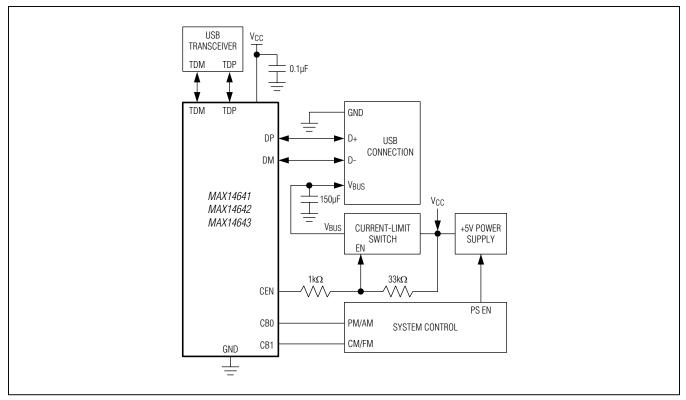

Figure 6. MAX14641/MAX14642/MAX14643 Peripheral Reset Applications

#### **Table 6. Forced Charging Modes**

| CHARGING MODE | DP PULLUP (k $\Omega$ ) | DP PULLDOWN ( $k\Omega$ ) | DM PULLUP (k $\Omega$ ) | DM PULLDOWN (k $\Omega$ ) |

|---------------|-------------------------|---------------------------|-------------------------|---------------------------|

| FM            | N/A                     | N/A                       | N/A                     | N/A                       |

| SS            | 30                      | 10                        | 30                      | 10                        |

| AP1           | 75                      | 49.9                      | 43.2                    | 49.9                      |

| AP2           | 43.2                    | 49.9                      | 75                      | 49.9                      |

#### **Forced Charger Modes**

The MAX14640–MAX14644/MAX14651 can be configured in different forced dedicated charging port (DCP) modes; V<sub>BUS</sub> is enabled and DP and DM are either shorted (FM) or connected to resistor-dividers (all other modes). <u>Table 6</u> summarizes the resistor-divider values in each forced mode.

# Automatic Detection with Remote Wake-Up Support

The MAX14640–MAX14644/MAX14651 feature automatic detection charger mode (AM1/AM2) for dedicated

chargers and USB masters. In automatic detection charger mode, the device monitors the voltages on DM and DP with resistor-dividers connected to determine the type of device attached.

If a USB-compliant device is connected, DP and DM are shorted together to commence charging. Once the charging device is removed, the short between DP and DM is disconnected and the resistor-divider is applied. A pulldown resistor on the shorted DP/DM node ensures that a disconnect is detected.

#### **USB Pass-Through Mode with CDP Emulation**

The MAX14640–MAX14644/MAX14651 feature a passthrough mode with CDP emulation (CM). This is to support the higher charging current capability during the passthrough mode in normal USB operation (S0 state). The peripheral device equipped with CDP detection capability can draw a charging current as defined in USB battery charger specification 1.2 when the charging host supports the CDP mode. This is a useful feature since most host USB transceivers do not have the CDP function. Table 7 summarizes the USB host power states.

#### Table 7. USB Host Power States

| STATE | DESCRIPTION                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------|

| S0    | System On                                                                                                              |

| S1    | Power to the CPU(s) and RAM is Maintained. Devices that do not indicate that they must remain on, may be powered down. |

| S2    | CPU is Powered Off                                                                                                     |

| S3    | Standby (Suspend to Ram)—System Memory Context is Maintained. All other system context is lost.                        |

| S4    | Hibernate—Platform Context is Maintained                                                                               |

| S5    | Soft Off                                                                                                               |

#### **Register Map/Register Descriptions**

| REGISTER | ADDR | TYPE | POR   | BIT7     | BIT6             | BIT5    | BIT4    | BIT3     | BIT2 | BIT1         | BIT0        |

|----------|------|------|-------|----------|------------------|---------|---------|----------|------|--------------|-------------|

| DeviceID | 0x00 | R    | 0x10* |          | CHIPID[3         | 8:0]    |         |          |      | CHIPREV[3:0] |             |

| Control1 | 0x01 | R/W  | 0x87  | FUO      | FUO              | FUO     | FUO     | FUO      | FUO  | FUO          | FUO         |

| Control2 | 0x02 | R/W  | 0x50  | LOW_PWR  | FUO              | FUO     | FUO     | FUO      | FUO  | DIS_CDP      | FUO         |

| Control3 | 0x03 | R/W  | 0xE9  | CEN_     | N_CNT[1:0] CEN_D |         |         | )]       |      | MODE_SEL[2   | 2:0]        |

| Control4 | 0x04 | R/W  | 0x00  | RFU      | RFU              | RFU     | RFU     | RFU      | RFU  | RFU          | RFU         |

| Control5 | 0x05 | R/W  | 0x7B  | INT_EN   | USB_SW           | [1:0]   | CEN_OUT | CEN_POL  | FUO  | RWU_DFT      | RWU_LS      |

| INT      | 0x06 | R    | 0x00  | CDP_DEVi | BYPASS_CDPi      | CDP_CNi | RFU     | USB_XFRi | RWUi | CEN_TOG_STi  | CEN_TOG_SPi |

| STATUS   | 0x07 | R    | 0x00  | CDP_DEVs | BYPASS_CDPs      | CDP_CNs | RFU     | USB_XFRs | RWUs | RFU          | CEN_TOG_SPs |

| MASK     | 0x08 | R/W  | 0x00  | CDP_DEVm | BYPASS_CDPm      | CDP_CNm | RFU     | USB_XFRm | RWUm | CEN_TOG_STm  | CEN_TOG_SPm |

FUO = Factory Use Only. Do not change from POR values.

RFU = Reserved for Future Use. Do not change from POR values.

\*Applies to the MAX14640; the MAX14651 POR is 0x20.

# USB Host Adapter Emulators

### **DeviceID Register**

| ADDRESS:     |              | 0x00             |                |                   |                |              |             |   |

|--------------|--------------|------------------|----------------|-------------------|----------------|--------------|-------------|---|

| MODE:        |              | Read Only        |                |                   |                |              |             |   |

| BIT          | 7            | 6                | 5              | 4                 | 3              | 2            | 1           | 0 |

| NAME         |              | CHIPI            | D[3:0]         |                   |                | CHIPR        | EV[3:0]     |   |

| RESET        | 0            | 0                | 0              | 1                 | 0              | 0            | 0           | 0 |

| CHIPID[3:0]  | The CHIPID[3 | 3:0] bits show i | nformation abo | out the version   | of the MAX146  | 640/MAX14651 |             |   |

| CHIPREV[3:0] | The CHIPREV  | /[3:0] bits show | information a  | bout the revision | on of the MAX1 | 4640/MAX146  | 51 silicon. |   |

### **Control1 Register**

| ADDRESS: |               | 0x01            |                  |           |     |     |     |     |

|----------|---------------|-----------------|------------------|-----------|-----|-----|-----|-----|

| MODE:    |               | Read/Write      |                  |           |     |     |     |     |

| BIT      | 7             | 6               | 5                | 4         | 3   | 2   | 1   | 0   |

| NAME     | FUO           | FUO             | FUO              | FUO       | FUO | FUO | FUO | FUO |

| RESET    | 1             | 0               | 0                | 0         | 0   | 1   | 1   | 1   |

| FUO      | Factory Use C | Dnly. Do not mo | odify from reset | t values. | ~   |     |     |     |

#### **Control2 Register**

| ADDRESS: |                                         | 0x02                                                                           |                                     |           |                  |                              |                  |   |  |  |

|----------|-----------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|-----------|------------------|------------------------------|------------------|---|--|--|

| MODE:    |                                         | Read/Write                                                                     |                                     |           |                  |                              |                  |   |  |  |

| BIT      | 7                                       | 6                                                                              | 5                                   | 4         | 3                | 2                            | 1                | 0 |  |  |

| NAME     | LOW_PWR FUO FUO FUO FUO FUO DIS_CDP FUC |                                                                                |                                     |           |                  |                              |                  |   |  |  |

| RESET    | 0                                       | 1                                                                              | 0                                   | 1         | 0                | 0                            | 0                | 0 |  |  |

| LOW_PWR  |                                         | 0/MAX14651 is                                                                  | s in normal ope<br>s in low-power i |           | uitry other than | the I <sup>2</sup> C interfa | ace is disabled. |   |  |  |

| DIS_CDP  | 0 = CDP sign                            | Disable CDP Signal.<br>0 = CDP signaling enabled<br>1 = CDP signaling disabled |                                     |           |                  |                              |                  |   |  |  |

| FUO      | Factory Use C                           | Only. Do not ma                                                                | odify from reset                    | t values. |                  |                              |                  |   |  |  |

# USB Host Adapter Emulators

#### **Control3 Register**

| ADDRESS:      |                                                                                                                                | 0x03                        |                              |                            |               |                                     |    |   |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|----------------------------|---------------|-------------------------------------|----|---|--|

| MODE:         |                                                                                                                                | Read/Write                  |                              |                            |               |                                     |    |   |  |

| BIT           | 7                                                                                                                              | 6 5 4 3                     |                              |                            |               | 2 1 0                               |    |   |  |

| NAME          | CEN_C                                                                                                                          | NT[1:0]                     |                              | ]                          | Ν             | NODE_SEL[2:0                        | )] |   |  |

| RESET         | 1                                                                                                                              | 1                           | 1                            | 0                          | 1             | 0                                   | 0  | 1 |  |

| CEN_CNT[1:0]  | 00 = CEN de<br>01 = CEN cy<br>10 = CEN as                                                                                      | asserted and cling disabled | CEN cycling o<br>between CB_ | disabled<br>transitions du |               | automatic cyclir<br>des and in AM r | •  |   |  |

| CEN_DEL[2:0]  | CEN Pulse D<br>000 = 125ms<br>001 = 250ms<br>010 = 350ms<br>011 = 500ms<br>100 = 750ms<br>101 = 1.0s<br>110 = 1.5s<br>111 = 2s |                             | now long V <sub>BL</sub>     | <sub>IS</sub> toggles last | outside of AM | I mode.                             |    |   |  |

| MODE_SEL[2:0] | Operating Mo<br>000 = AM2<br>001 = PM<br>010 = FM<br>011 = CM<br>100 = AM1<br>101 = AP1<br>110 = AP2<br>111 = SS               | ode Control.                |                              |                            |               |                                     |    |   |  |

### **Control4 Register**

| ADDRESS: |              | 0x04       |     |     |     |     |     |     |

|----------|--------------|------------|-----|-----|-----|-----|-----|-----|

| MODE:    |              | Read/Write |     |     |     |     |     |     |

| BIT      | 7            | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

| NAME     | RFU          | RFU        | RFU | RFU | RFU | RFU | RFU | RFU |

| RESET    | 0            | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| RFU      | Reserved for | Future Use |     |     |     | •   | •   |     |

# USB Host Adapter Emulators

## Control5 Register

| ADDRESS:    |                                                                                            | 0x05                                                                 |                     |                         |                |              |                  |            |  |  |  |

|-------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------|-------------------------|----------------|--------------|------------------|------------|--|--|--|

| MODE:       |                                                                                            | Read/Write                                                           |                     |                         |                |              |                  |            |  |  |  |

| BIT         | 7                                                                                          | 6                                                                    | 5                   | 4                       | 3              | 2            | 1                | 0          |  |  |  |

| NAME        | INT_EN                                                                                     | INT_EN USB_SW[1:0] CEN_OUT CEN_POL FUO RWU_DFT RWU_L                 |                     |                         |                |              |                  |            |  |  |  |

| RESET       | 0                                                                                          | 1                                                                    | 1                   | 1                       | 1              | 0            | 1                | 1          |  |  |  |

| INT_EN      | 0 = Interrupt of                                                                           | Interrupt Enable.<br>0 = Interrupt disabled<br>1 = Interrupt enabled |                     |                         |                |              |                  |            |  |  |  |

| USB_SW[1:0] | output are dis<br>00 = DP/DM i<br>01 = DP/DM o<br>10 = DP/DM o                             | abled.                                                               | DP/TDM<br>DP/DCP/AM | circuitry               | d open (00) or | closed (01), | the state machir | ne and CEN |  |  |  |

| CEN_OUT     | $0 = \overline{INT}$ output                                                                | ction Select. C<br>It is used as in<br>It is used as C               | terrupt             | nction of the INT       | pin.           |              |                  |            |  |  |  |

| CEN_POL     | 0 = CEN/INT                                                                                | rity Select. Co<br>output is active<br>output is active              | e-low CEN/IN        |                         | ÎNT output.    |              |                  |            |  |  |  |

| FUO         | Factory Use 0                                                                              | Dnly. Do not m                                                       | odify from res      | et value.               |                |              |                  |            |  |  |  |

| RWU_DFT     | Remote Wake-Up Default.         0 = Remote wake-up is off         1 = Remote wake-up is on |                                                                      |                     |                         |                |              |                  |            |  |  |  |

| RWU_LS      | 0 = Remote w                                                                               | e-Up for Low-S<br>vake-up for bo<br>vake-up for onl                  | th FS/HS and        | lect.<br>LS USB device: | 5              |              |                  |            |  |  |  |

# USB Host Adapter Emulators

#### Interrupt (INT) Register

| ADDRESS:    |                                                               | 0x06                   |                 |             |                    |                         |                             |                           |

|-------------|---------------------------------------------------------------|------------------------|-----------------|-------------|--------------------|-------------------------|-----------------------------|---------------------------|

| MODE:       |                                                               | Read Only              |                 |             |                    |                         |                             |                           |

| BIT         | 7                                                             | 6                      | 5               | 4           | 3                  | 2                       | 1                           | 0                         |

| NAME        | CDP_DEVi                                                      | BYPASS_CDPi            | CDP_CNi         | RFU         | USB_XFRi           | RWUi                    | CEN_TOG_STi                 | CEN_TOG_SPi               |

| RESET       | 0                                                             | 0                      | 0               | 0           | 0                  | 0                       | 0                           | 0                         |

| CDP_DEVi    |                                                               | procedure in CM<br>upt |                 | DEVi is set | when a CDP de      | evice is de             | tected following tl         | ne CDP                    |

| BYPASS_CDPi | Bypass CDP<br>0 = No interr<br>1 = Interrupt                  | upt                    | nterrupt. BYP   | ASS_CDPi    | is set when the    | e CDP hand              | dshake procedure            | e is bypassed.            |

| CDP_CNi     | CDP Connec<br>0 = No interr<br>1 = Interrupt                  | upt                    | . CDP_CNi is    | set whene   | ver a CDP conr     | nection che             | eck is in progress          |                           |

| RFU         | Reserved for                                                  | Future Use             |                 |             |                    |                         |                             |                           |

| USB_XFRi    | USB Session<br>connected to<br>0 = No interr<br>1 = Interrupt | o TDP/TDM.<br>upt      | KFRi is set whe | en there is | USB data dete      | cted in CM              | 1 mode and DP/D             | M are                     |

| RWUi        | Remote Wak<br>0 = No interr<br>1 = Interrupt                  | upt                    | rupt. RWUi is   | set whene   | ver a remote w     | ake-up is p             | performed in AM r           | node.                     |

| CEN_TOG_STI | CEN Toggle<br>disabled.<br>0 = No interr<br>1 = Interrupt     | upt                    | errupt. CEN_T   | OG_STi is   | set at the start o | of a V <sub>BUS</sub> t | oggle, when V <sub>BU</sub> | <sub>S</sub> is first     |

| CEN_TOG_SPi | CEN Toggle<br>disabled.<br>0 = No interr<br>1 = Interrupt     | upt                    | errupt. CEN_T   | OG_SPi is   | set at the end o   | of a V <sub>BUS</sub> t | oggle, when V <sub>BU</sub> | <sub>S</sub> is no longer |

# USB Host Adapter Emulators

### STATUS Register

| ADDRESS:    |                                                                                                                                        | 0x07                                                                                                                                                                                                                    |             |                |                           |               |             |                             |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|---------------------------|---------------|-------------|-----------------------------|--|--|

| MODE:       |                                                                                                                                        | Read Only                                                                                                                                                                                                               |             |                |                           |               |             |                             |  |  |

| BIT         | 7                                                                                                                                      | 6                                                                                                                                                                                                                       | 5           | 4              | 3                         | 2             | 1           | 0                           |  |  |

| NAME        | CDP_DEVs                                                                                                                               | BYPASS_CDPs                                                                                                                                                                                                             | CDP_CNs     | RFU            | USB_XFRs                  | RWUs          | RFU         | CEN_TOG_SPs                 |  |  |

| RESET       | 0                                                                                                                                      | 0                                                                                                                                                                                                                       | 0           | 0              | 0                         | 0             | 0           | 0                           |  |  |

| CDP_DEVs    | procedure in<br>0 = CDP dev                                                                                                            | CDP Device Detect Status. CDP_DEVs is set when a CDP device is detected following the CDP handshake procedure in CM mode and cleared when it is disconnected.<br>D = CDP device not detected<br>1 = CDP device detected |             |                |                           |               |             |                             |  |  |

| BYPASS_CDPs | 0 = CDP sigr                                                                                                                           | Running Status. I<br>naling used<br>naling bypassed                                                                                                                                                                     | BYPASS_CDP  | s is set wher  | n the CDP hand            | dshake proce  | edure is by | passed.                     |  |  |

| CDP_CNs     | 0 = No CDP                                                                                                                             | t Status. CDP_CN<br>connection check<br>nection check in                                                                                                                                                                | in progress | a CDP conn     | ection attempt            | is in progres | SS.         |                             |  |  |

| RFU         | Reserved for                                                                                                                           | Future Use                                                                                                                                                                                                              |             |                |                           |               |             |                             |  |  |

| USB_XFRs    | to TDP/TDM.<br>0 = No USB s                                                                                                            | Status. USB_XFF<br>session in progres<br>sion in progress                                                                                                                                                               |             | there is USE   | 3 data detectec           | I in CM mode  | e and DP/D  | 0M are connected            |  |  |

| RWUs        | Remote Wake-Up Status. RWUs is set while a remote wake-up is in progress in AM mode.<br>0 = Not waiting for RWU<br>1 = Waiting for RWU |                                                                                                                                                                                                                         |             |                |                           |               |             |                             |  |  |

| CEN_TOG_SPs | 0 = V <sub>BUS</sub> tog                                                                                                               | Status. CEN_TOG<br>gle in progress<br>gle not in progres                                                                                                                                                                |             | t the start of | a V <sub>BUS</sub> toggle | and set at t  | he end of t | ne V <sub>BUS</sub> toggle. |  |  |

# USB Host Adapter Emulators

#### MASK Register

| ADDRESS:    |                                                                                                                                                                      | 0x08        |         |     |          |      |             |             |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-----|----------|------|-------------|-------------|

| MODE:       | Read/Write                                                                                                                                                           |             |         |     |          |      |             |             |

| BIT         | 7                                                                                                                                                                    | 6           | 5       | 4   | 3        | 2    | 1           | 0           |

| NAME        | CDP_DEVm                                                                                                                                                             | BYPASS_CDPm | CDP_CNm | RFU | USB_XFRm | RWUm | CEN_TOG_STm | CEN_TOG_SPm |

| RESET       | 0                                                                                                                                                                    | 0           | 0       | 0   | 0        | 0    | 0           | 0           |

| CDP_DEVm    | CDP Device Detect Status Interrupt Mask. Prevents an interrupt from being generated in CDP_DEVi when CDP_DEVs is set to 1.<br>0 = Masked<br>1 = Not masked           |             |         |     |          |      |             |             |

| BYPASS_CDPm | Bypass CDP Running Status Interrupt Mask. Prevents an interrupt from being generated in BYPASS_CDPi<br>when BYPASS_CDPs is set to 1.<br>0 = Masked<br>1 = Not masked |             |         |     |          |      |             |             |

| CDP_CNm     | CDP Connect Status Interrupt Mask. Prevents an interrupt from being generated in CDP_CNi when CDP_CNs<br>is set to 1.<br>0 = Masked<br>1 = Not masked                |             |         |     |          |      |             |             |

| RFU         | Reserved for Future Use                                                                                                                                              |             |         |     |          |      |             |             |

| USB_XFRm    | USB Session Interrupt Mask. Prevents an interrupt from being generated in USB_XFRi when USB_XFRs is set<br>to 1.<br>0 = Masked<br>1 = Not masked                     |             |         |     |          |      |             |             |

| RWUm        | Remote Wake-Up Status Interrupt Mask. Prevents an interrupt from being generated in RWUi when RWUs is<br>set to 1.<br>0 = Masked<br>1 = Not masked                   |             |         |     |          |      |             |             |

| CEN_TOG_STm | CEN Toggle Start Monitor Interrupt Mask. Prevents an interrupt from being generated in CEN_TOG_STi when<br>CEN_TOG_STs is set to 1.<br>0 = Masked<br>1 = Not masked  |             |         |     |          |      |             |             |

| CEN_TOG_SPm | CEN Toggle Stop Monitor Interrupt Mask. Prevents an interrupt from being generated in CEN_TOG_SPi when<br>CEN_TOG_SPs is set to 1.<br>0 = Masked<br>1 = Not masked   |             |         |     |          |      |             |             |

### **Applications Information**

#### I<sup>2</sup>C Interface

The MAX14640/MAX14651 contain an I<sup>2</sup>C-compatible interface for data communication with a host controller (SCL and SDA). The interface supports a clock frequency of up to 400kHz. SCL and SDA require pullup resistors that are connected to a positive supply.

#### START, STOP, and Repeated START Conditions

When writing to the MAX14640/MAX14651 using I<sup>2</sup>C, the master sends a START condition (S) followed by the MAX14640/MAX14651 I<sup>2</sup>C address. After the address, the master sends the register address of the register that is to be programmed. The master then ends communication by issuing a STOP condition (P) to relinquish control of the bus, or a Repeated START condition (Sr) to communicate to another I<sup>2</sup>C slave. See Figure 7.

#### **Slave Address**

The MAX14640 and MAX14651 are the I<sup>2</sup>C versions that have different slave addresses (<u>Table 8</u>). Set the read/ write bit high to configure the MAX14640/MAX14651 to read mode. Set the read/write bit low to configure the MAX14640/MAX14651 to write mode. The address is the first byte of information sent to the MAX14640/MAX14651 after the START condition.

#### **Bit Transfer**

One data bit is transferred on the rising edge of each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the *START, STOP, and Repeated START Conditions* section). Both SDA and SCL remain high when the bus is not active.

Figure 7. I<sup>2</sup>C START, STOP, and Repeated START Conditions

#### Table 8. I<sup>2</sup>C Slave Addresses

|                |      | MAX14640  | MAX14651 |           |  |

|----------------|------|-----------|----------|-----------|--|

| ADDRESS FORMAT | HEX  | BINARY    | HEX      | BINARY    |  |

| 7-Bit Slave ID | 0x35 | 011 0101  | 0x15     | 001 0101  |  |

| Write Address  | 0x6A | 0110 1010 | 0x2A     | 0010 1010 |  |

| Read Address   | 0x6B | 0110 1011 | 0x2B     | 0010 1011 |  |

### USB Host Adapter Emulators

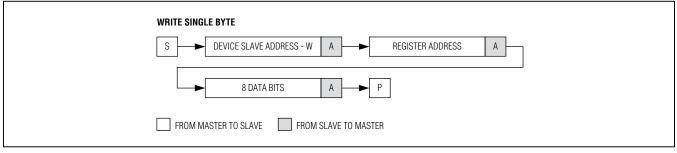

#### Single-Byte Write

In this operation, the master sends an address and two data bytes to the slave device (Figure 8). The following procedure describes the single-byte write operation:

- 1) The master sends a START condition.

- 2) The master sends the 7-bit slave address plus a write bit (low).

- 3) The addressed slave asserts an ACK on the data line.

- 4) The master sends the 8-bit register address.

- 5) The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6) The master sends eight data bits.

- 7) The slave asserts an ACK on the data line.

- 8) The master generates a STOP condition.

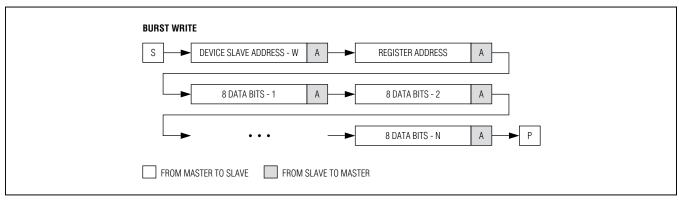

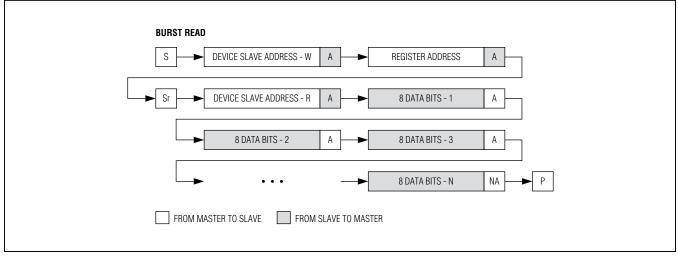

#### **Burst Write**

In this operation, the master sends an address and multiple data bytes to the slave device (Figure 9). The slave device automatically increments the register address after each data byte is sent, unless the register being accessed is 0x00, in which case the register address remains the same. The following procedure describes the burst write operation:

- 1) The master sends a START condition.

- 2) The master sends the 7-bit slave address plus a write bit (low).

- 3) The addressed slave asserts an ACK on the data line.

- 4) The master sends the 8-bit register address.

- 5) The slave asserts an ACK on the data line only if the address is valid (NAK if not).

- 6) The master sends eight data bits.

- 7) The slave asserts an ACK on the data line.

- 8) Repeat 6 and 7 (N 1) times.

- 9) The master generates a STOP condition.

Figure 8. Write-Byte Sequence

Figure 9. Burst Write Sequence

### **USB Host Adapter Emulators**

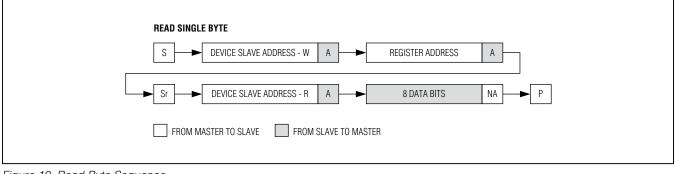

#### Single-Byte Read

In this operation, the master sends an address plus two data bytes and receives one data byte from the slave device (Figure 10). The following procedure describes the single-byte read operation:

- 1) The master sends a START condition.

- 2) The master sends the 7-bit slave address plus a write bit (low).

- 3) The addressed slave asserts an ACK on the data line.

- 4) The master sends the 8-bit register address.