# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

#### **General Description**

The MAX14571/MAX14572/MAX14573 adjustable overvoltage and overcurrent-protection devices are ideal to protect systems against positive and negative input voltage faults up to  $\pm 40 \text{V}$  and feature low  $100 \text{m}\Omega(\text{typ})$  R<sub>ON</sub> FETs.

The overvoltage-protector (OVP) feature protects voltages between 6V and 36V, while the undervoltage-protector (UVP) feature protects voltages between 4.5V and 24V. The overvoltage-lockout (OVLO) and undervoltage-lockout (UVLO) thresholds are set using optional external resistors. The factory-preset internal OVLO threshold is 33V (typ) and the preset internal UVLO threshold is 19.2V (typ).

The ICs also feature programmable current-limit protection up to 4.2A. Once current reaches the threshold, the MAX14571 turns off after the 20.7ms (typ) blanking time and stays off during the retry period. The MAX14572 latches off after the blanking time, and the MAX14573 limits the current continuously. In addition, these devices feature reverse current and thermal-shutdown protection.

The ICs are available in a small 14-pin TSSOP (5mm  $\times$  6.5mm) package and are specified over the extended  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

#### **Benefits and Features**

- Integrated Protection Increases System Reliability

- Adjustable OVLO and UVLO Thresholds (±3% Accurate Preset Thresholds)

- Automatic Internal and External Selection

- Programmable Forward Current Limit (Adjustable Up to 4.2A) with ±15% Accuracy

- Thermal-Shutdown Protection

- 100mΩ (typ) On-Resistance FET

- Special Features Facilitate Designs for Industrial Applications

- Wide 4.5V to 36V Operating Input Range

- Reverse-Current Flow Option for Inductive Loads

- Independent Microprocessor Enable Input (EN) and High-Voltage-Capable Input (HVEN)

#### **Applications**

- Industrial Equipment

- Consumer Electronics

- Marine Equipment

- Battery-Powered Applications

Ordering Information appears at end of data sheet.

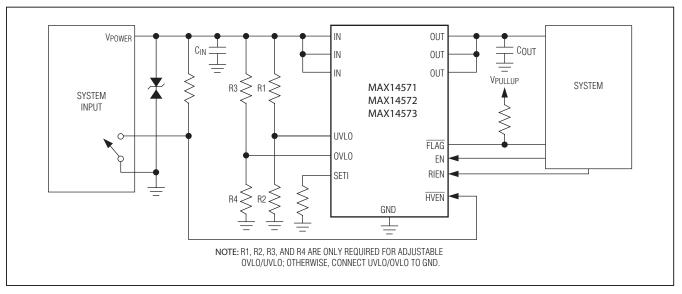

### **Typical Operating Circuit**

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

#### **Absolute Maximum Ratings**

| (All voltages referenced to GND.)                | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|--------------------------------------------------|-------------------------------------------------------|

| IN, <del>HVEN</del> 40V to +40V                  | TSSOP (derate 25.6mW/°C above +70°C) 2051.3mW         |

| IN to OUT40V to +40V                             | Operating Temperature Range40°C to +85°C              |

| OUT0.3V to +40V                                  | Junction Temperature+150°C                            |

| OVLO, UVLO, FLAG, EN, RIEN0.3V to +6.0V          | Storage Temperature Range65°C to +150°C               |

| Current into IN (DC Operating) (Note 1)4.2A      | Lead Temperature (soldering, 10s)+300°C               |

| SETI0.3V to Min (V <sub>IN</sub> , 1.22V) + 0.3V | Soldering Temperature (reflow)+260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: DC current is also limited by the thermal design of the system.

### **Package Information**

| PACKAGE TYPE: 14 TSSOP                 |                |  |  |  |

|----------------------------------------|----------------|--|--|--|

| Package Code                           | U14E+3         |  |  |  |

| Outline Number                         | <u>21-0108</u> |  |  |  |

| Land Pattern Number                    | 90-0119        |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | +39°C/W        |  |  |  |

| Junction to Case $(\theta_{JC})$       | +3°C/W         |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed informa¬tion on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = 4.5V \text{ to } 36V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 24V, R_{SETI} = 12k\Omega, T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                        | SYMBOL              | CONDITIONS                                 | MIN  | TYP  | MAX  | UNITS |

|----------------------------------|---------------------|--------------------------------------------|------|------|------|-------|

| IN Voltage Range                 | V <sub>IN</sub>     |                                            | 4.5  |      | 36   | V     |

| Shutdown Input Current           | I <sub>SHDN</sub>   | $V_{EN} = 0V, V_{\overline{HVEN}} = 5V$    |      |      | 15   | μΑ    |

| Shutdown Output Current          | l <sub>OFF</sub>    | $V_{OUT} = 0V$                             |      |      | 2    | μA    |

| Reverse Input Current            | I <sub>IN_RVS</sub> | $V_{IN} = -40V$ , $V_{OUT} = V_{GND} = 0V$ | -35  |      |      | μΑ    |

| Supply Current                   | I <sub>IN</sub>     | $V_{IN} = 15V$ , $R_{ISET} = 12k\Omega$    |      | 490  | 700  | μA    |

|                                  |                     | V <sub>IN</sub> rising                     | 32   | 33   | 34   | .,,   |

| Internal Overvoltage Trip Level  | V <sub>OVLO</sub>   | V <sub>IN</sub> falling                    |      | 32   |      | V     |

| Internal Undervoltage Trip Level | .,                  | V <sub>IN</sub> falling                    | 17.5 | 18.5 | 19.5 | .,    |

|                                  | V <sub>UVLO</sub>   | V <sub>IN</sub> rising                     | 18.2 | 19.2 | 20.2 | V     |

| Overvoltage-Lockout Hysteresis   |                     | % of typical OVLO                          |      | 3    |      | %     |

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

### **Electrical Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 36V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 24V, R_{SETI} = 12k\Omega, T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                | SYMBOL                                                                     | CONDITIONS                                                                                    | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| External OVLO Adjustment Range           |                                                                            | (Note 3)                                                                                      | 6     |       | 36    | V     |

| External OVLO Select Voltage             | Vovlosel                                                                   |                                                                                               | 0.3   |       | 0.50  | V     |

| External OVLO Leakage Current            | lovlo_leak                                                                 | V <sub>OVLO</sub> < 1.2V (Note 4)                                                             | -100  |       | +100  | nA    |

| External UVLO Adjustment Range           |                                                                            |                                                                                               | 4.5   |       | 24    | V     |

| External UVLO Select Voltage             | V <sub>OVLOSEL</sub>                                                       |                                                                                               | 0.3   |       | 0.50  | V     |

| External UVLO Leakage Current            | I <sub>UVLO</sub> LEAK                                                     | (Note 4)                                                                                      | -100  |       | +100  | nA    |

| BG Reference Voltage                     | $V_{BG}$                                                                   |                                                                                               | 1.186 | 1.210 | 1.234 | V     |

| INTERNAL FETs                            |                                                                            |                                                                                               |       |       |       |       |

| Internal FET On-Resistance               | R <sub>ON</sub>                                                            | $I_{LOAD} = 100 \text{mA}, V_{IN} \ge 8 \text{V}$                                             |       | 100   | 160   | mΩ    |

| Current-Limit Adjustment Range           | I <sub>LIM</sub>                                                           | (Notes 4, 5)                                                                                  | 0.7   |       | 4.2   | А     |

| Current-Limit Accuracy                   |                                                                            |                                                                                               | -15   |       | +15   | %     |

| FLAG Assertion Drop Voltage<br>Threshold | V <sub>FA</sub>                                                            | Increase (V <sub>IN</sub> - V <sub>OUT</sub> ) drop until FLAG asserts, V <sub>IN</sub> = 24V |       | 560   |       | mV    |

| Reverse Current Blocking Threshold       | V <sub>RIB</sub>                                                           | V <sub>OUT</sub> - V <sub>IN</sub>                                                            | 40    | 100   | 160   | mV    |

| Reverse Blocking Leakage Current         | I <sub>RBL</sub>                                                           | V <sub>OUT</sub> - V <sub>IN</sub> > 160mV, current into OUT                                  |       | 400   | 600   | μΑ    |

| FLAG OUTPUT                              |                                                                            |                                                                                               |       |       |       |       |

| FLAG Output Logic-Low Voltage            |                                                                            | I <sub>SINK</sub> = 1mA                                                                       |       |       | 0.4   | V     |

| FLAG Output Leakage Current              |                                                                            | V <sub>IN</sub> = V <sub>FLAG</sub> = 5V, FLAG desasserted                                    |       |       | 2     | μΑ    |

| LOGIC INPUT                              |                                                                            |                                                                                               |       |       |       |       |

| HVEN Threshold Voltage                   | V <del>HVEN_TH</del>                                                       |                                                                                               | 1     | 2     | 3.5   | V     |

| HVEN Threshold Hysteresis                |                                                                            |                                                                                               |       | 2     |       | %     |

| HVEN Input Leakage Current               | I <del>HVEN</del> _LEAK                                                    | V <sub>HVEN</sub> = 36V                                                                       |       | 26    | 40    | μΑ    |

| HVEN Input Reverse Leakage<br>Current    | HVEN_RLEAK                                                                 | $V_{IN} = V_{\overline{HVEN}} = -36V$                                                         | -45   | -27   |       | μΑ    |

| EN, RIEN Input Logic-High                | V <sub>IH</sub>                                                            |                                                                                               | 1.4   |       |       | V     |

| EN, RIEN Input Logic-Low                 | V <sub>IL</sub>                                                            |                                                                                               |       |       | 0.4   | V     |

| EN, RIEN Input Leakage Current           | I <sub>EN_LEAK</sub> , I <sub>RIEN_LEAK</sub>                              | $V_{EN} = V_{RIEN} = 5.0V$                                                                    | -1    |       | +1    | μΑ    |

| THERMAL PROTECTION                       |                                                                            |                                                                                               |       |       |       |       |

| Thermal Shutdown                         | T <sub>JC_MAX</sub>                                                        | Low-to-high temperature                                                                       |       | 150   |       | °C    |

| Thermal-Shutdown Hysteresis              | T <sub>JC_HYST</sub>                                                       | High-to-low temperature                                                                       |       | 30    |       | °C    |

| TIMING CHARACTERISTICS (Note             |                                                                            |                                                                                               |       |       |       |       |

| Switch Turn-On Time                      | From OFF to IN, see Table 1. $R_{LOAD} = 240\Omega$ , $C_{OUT} = 470\mu$ F |                                                                                               |       | ms    |       |       |

| Switch Turn-Off Time                     | toff                                                                       | $R_{LOAD} = 47\Omega$                                                                         |       | 3     |       | μs    |

### **Electrical Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 36V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = 24V, R_{SETI} = 12k\Omega, T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                        | SYMBOL               | CONDITIONS                                                                                                     | MIN  | TYP  | MAX  | UNITS |

|----------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Overvoltage Switch Turn-Off Time | t <sub>OFF_OVP</sub> | $V_{IN} > V_{OVLO}$ to $V_{OUT} = 80\%$ of $V_{OVLO}$ , $R_{LOAD} = 47\Omega$ , $R_{SETI} = 10k\Omega$         |      | 3    |      | μs    |

| Overcurrent Switch Turn-Off Time | toff_ocp             | $I_{IN} > I_{LIM}$ , after $t_{BLANK}$ , $I_{LIM} = 1A$                                                        |      | 3    |      | μs    |

| IN Debounce Time                 | t <sub>DEB</sub>     | V <sub>IN</sub> changes from 0V to greater than V <sub>UVLO</sub> to V <sub>OUT</sub> = 10% of V <sub>IN</sub> | 15.0 | 16.7 | 18.4 | ms    |

| Blanking Time                    | t <sub>BLANK</sub>   |                                                                                                                | 18.6 | 20.7 | 22.8 | ms    |

| Autoretry Time                   | t <sub>RETRY</sub>   | After blanking time from I <sub>OUT</sub> > I <sub>LIM</sub> to FLAG clear (deassertion) (Note 7)              | 540  | 600  | 660  | ms    |

| ESD PROTECTION                   |                      |                                                                                                                |      |      |      |       |

| IN                               |                      | Human Body Model, IN bypassed to GND with a 1µF low-ESR ceramic capacitor                                      |      | ±15  |      | kV    |

- **Note 2:** All units are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design and characterization; not production tested.

- Note 3: Not production tested, user settable. See overvoltage/undervoltage lockout instructions.

- Note 4: Guaranteed by design; not production tested. UVLO and OVLO are internally clamped to BG reference voltage.

- Note 5: The current limit can be set below 700mA with a decreased accuracy.

- Note 6: All timing is measured using 20% and 80% levels.

- Note 7: The ratio between the autoretry time and blanking time is fixed and equal to 30.

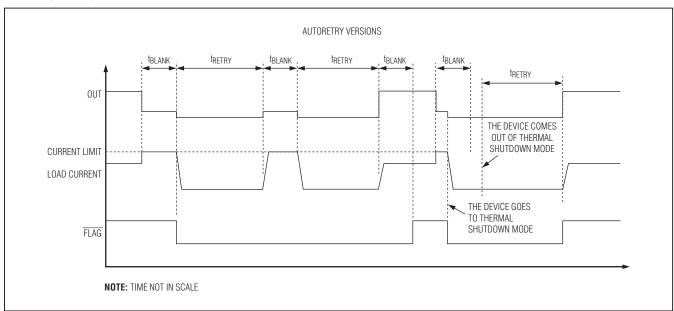

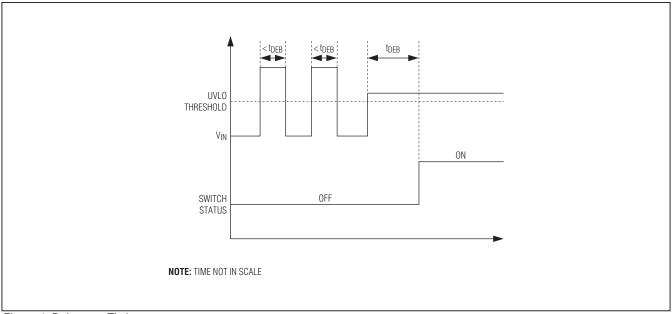

#### **Timing Diagrams**

Figure 1. Autoretry Fault Diagram

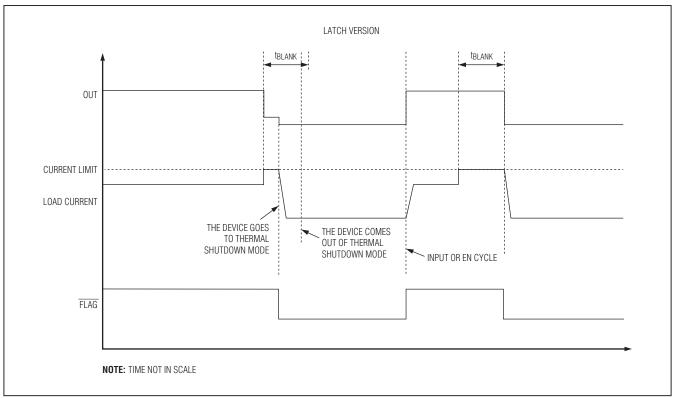

### **Timing Diagrams (continued)**

Figure 2. Latch-Off Fault Diagram

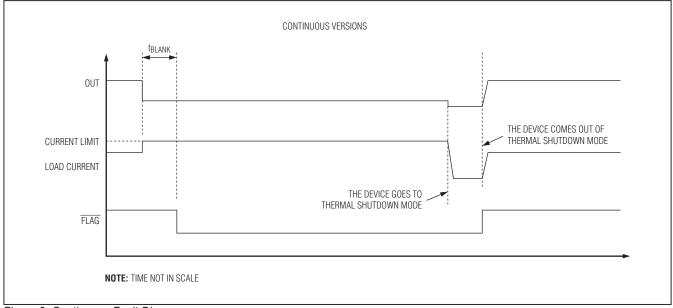

Figure 3. Continuous Fault Diagram

### **Timing Diagrams (continued)**

Figure 4. Debounce Timing

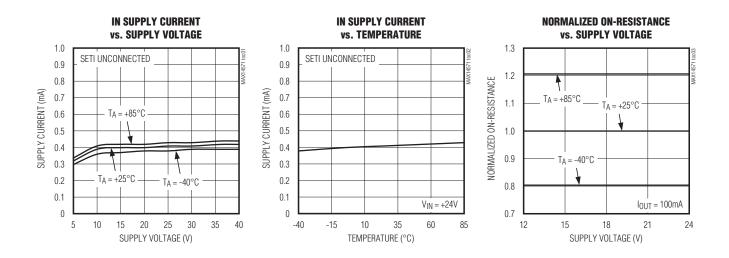

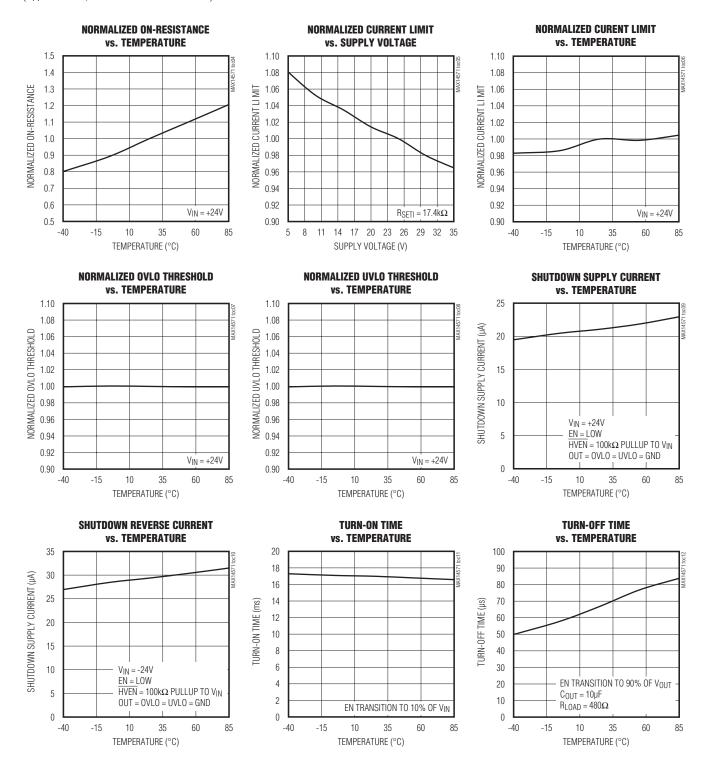

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Typical Operating Characteristics (continued)**

$(T_A = +25$ °C, unless otherwise noted.)

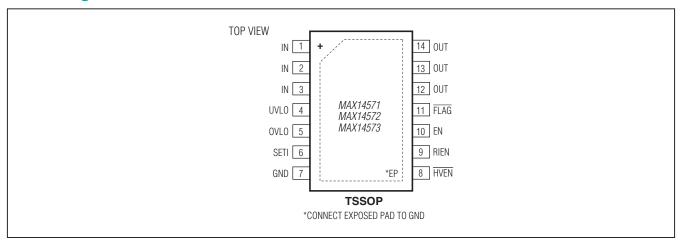

### **Pin Configuration**

### **Pin Description**

| PIN        | NAME | FUNCTION                                                                                                                                                                                                                                                                                            |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3    | IN   | Overvoltage-Protection Input. Bypass IN to GND with a $1\mu F$ ceramic capacitor placed as close as possible to the device. Use a $1\mu F$ , low-ESR ceramic capacitor to enable $\pm 15kV$ (HBM) ESD protection on IN. For hot-plug applications, see the <i>Applications Information</i> section. |

| 4          | UVLO | Externally Programmable Undervoltage-Lockout Threshold. Connect UVLO to GND to use the default internal UVLO threshold. Connect UVLO to an external resistor-divider to define a threshold externally and override the preset internal UVLO threshold.                                              |

| 5          | OVLO | Externally Programmable Overvoltage-Lockout Threshold. Connect OVLO to GND to use the default internal OVLO threshold. Connect OVLO to an external resistor-divider to define a threshold externally and override the preset internal OVLO threshold.                                               |

| 6          | SETI | Overload Current-Limit Adjust. Connect a resistor from SETI to GND to program the overcurrent limit. If SETI is unconnected, the current limit is set to 0A. If SETI is connected to GND, the FETs turn off and FLAG is asserted. Do not connect more than 10pF to SETI.                            |

| 7          | GND  | Ground                                                                                                                                                                                                                                                                                              |

| 8          | HVEN | Active-Low Enable Input. HVEN is a high-voltage-capable enable input. Drive HVEN low for normal operation. Drive HVEN high to disable the device. HVEN has up to 36V overvoltage protection at the input (Table 1).                                                                                 |

| 9          | RIEN | Reverse-Current Enable Input. Connect RIEN to GND to disable the reverse-current flow protection. Connect RIEN to logic-high to activate the reverse-current flow protection.                                                                                                                       |

| 10         | EN   | Active-High Enable Input. Drive EN high for normal operation. Drive EN low to disable the device (Table 1).                                                                                                                                                                                         |

| 11         | FLAG | Open-Drain, Fault Indicator Output. FLAG goes low when the fault duration exceeds the blanking time, reverse current is detected, thermal-shutdown mode is active, OVLO threshold is reached, or SETI is connected to GND.                                                                          |

| 12, 13, 14 | OUT  | Output Voltage. Output of internal FETs. Bypass OUT to GND with a 1µF ceramic capacitor placed as close as possible to the device. For a long output cable or inductive lead, see the <i>Applications Information</i> section.                                                                      |

| _          | EP   | Exposed Pad. Internally connected to GND. Connect EP to a large ground plane to maximize thermal performance. Do not use EP as the single GND connection.                                                                                                                                           |

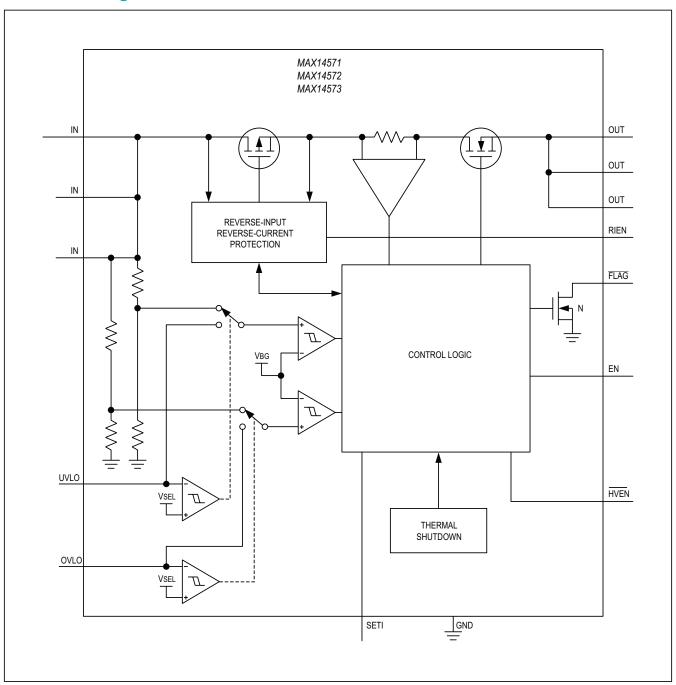

### **Functional Diagram**

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

#### **Detailed Description**

The MAX14571/MAX14572/MAX14573 are adjustable overvoltage- and overcurrent-protection devices designed to protect systems against positive and negative input voltage faults up to  $\pm 40$ V, and feature low  $100 m\Omega$  (typ) on-resistance FETs. If the input voltage exceeds the OVLO threshold or falls below the UVLO, the internal FETs are turned off to prevent damage to the protected components. If the OVLO or the UVLO pin is set below the external OVLO or UVLO select thresholds (VOVLOSEL and VUVLOSEL), the device automatically selects the internal  $\pm 3\%$  (typ) accurate trip thresholds. The internal OVLO threshold is preset to 33V (typ), and the internal UVLO threshold is preset to 19.2V (typ).

The ICs feature programmable current-limit protection up to 4.2A. Once current reaches the threshold, the MAX14571 turns off after 20.7ms (typ) blanking time and stays off during the retry period. The MAX14572 latches off after the blanking time, and the MAX14573 limits the current continuously.

#### **Programmable Current Limit/Threshold**

A resistor from SETI to GND sets the current limit/ threshold for the switch (see the <u>Setting the Current Limit/Threshold</u> section). If the output current is limited at the current threshold value for a time equal to or longer than t<sub>BLANK</sub>, the output FLAG asserts and the MAX14571 enters the autoretry mode, the MAX14572 latches off the switch, and the MAX14573 enters the continuous current-limit mode.

#### Autoretry (MAX14571)

When the current threshold is reached, the  $t_{BLANK}$  timer begins counting. The  $\overline{FLAG}$  asserts if the overcurrent condition is present for  $t_{BLANK}$ . The timer resets if the overcurrent condition disappears before  $t_{BLANK}$  has elapsed. A retry time delay,  $t_{RETRY}$ , is started immediately after  $t_{BLANK}$  has elapsed and during  $t_{RETRY}$  time, the FETs are off. At the end of  $t_{RETRY}$ , the FETs are turned on again. If the fault still exists, the cycle is repeated and the  $\overline{FLAG}$  stays low. When the fault is removed, the FETs stay on. If the die temperature exceeds +150°C (typ) due to self-heating, the MAX14571 enables thermal shutdown until the die temperature drops by approximately 30°C (Figure 1).

The autoretry feature reduces the system power in case of overcurrent or short-circuit conditions. During  $t_{BLANK}$  time, when the switch is on, the supply current is held at the current limit. During  $t_{RETRY}$  time, when the switch

is off, there is no current through the switch. Thus, the output current is much less than the programmed current limit. Calculate the average output current using the following equation:

$$I_{LOAD} = I_{LIM} \left[ \frac{t_{BLANK}}{t_{BLANK} + t_{RETRY}} \right]$$

With a 20.7ms (typ)  $t_{BLANK}$  and 600ms (typ)  $t_{RETRY}$ , the duty cycle is 3.3%, resulting in a 96.7% power savings.

#### Latch-Off (MAX14572)

When the current threshold is reached, the  $t_{BLANK}$  timer begins counting. The  $\overline{FLAG}$  asserts if the overcurrent condition is present for  $t_{BLANK}$ . The timer resets when the overcurrent condition disappears before  $t_{BLANK}$  has elapsed. The switch turns off and stays off if the overcurrent condition continues beyond the blanking time. To reset the switch, either toggle the control logic EN or  $\overline{HVEN}$  or cycle the input voltage. If the die temperature exceeds +150°C (typ) due to self-heating, the MAX14572 latches off (Figure 2).

#### **Continuous Current Limit (MAX14573)**

When the current threshold is reached, the MAX14573 limits the output current to the programmed current limit. The  $\overline{\text{FLAG}}$  asserts if the overcurrent condition is present for  $t_{\text{BLANK}}$  and deasserts when the overload condition is removed. If the die temperature exceeds +150°C (typ) due to self-heating, the MAX14573 enables thermal shutdown until the die temperature drops by approximately 30°C (Figure 3).

#### Reverse-Current Enable (RIEN)

This feature disables the reverse-current protection and enables reverse-current flow from OUT to IN. The reverse-current enable feature is useful in applications with inductive loads.

#### **Fault Flag Output**

FLAG is an open-drain fault indicator output and requires an external pullup resistor to a DC supply. FLAG goes low when any of the following conditions occur:

- The blanking time has elapsed.

- The reverse-current protection has tripped.

- The die temperature exceeds +150°C.

- SETI is connected to ground.

- · OVLO threshold is reached.

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

#### **Thermal-Shutdown Protection**

The devices have a thermal-shutdown feature to protect them from overheating. The devices turn off and the FLAG asserts when the junction temperature exceeds +150°C (typ). The devices exit thermal shutdown and resume normal operation after the junction temperature cools by 30°C (typ), except for the MAX14572, which remains latched off.

The thermal limit behaves similarly to the current limit. For the MAX14571 (autoretry), the thermal limit works with the autoretry timer. When the device comes out of the thermal limit, it starts after the retry time. For the MAX14572 (latch off), the device latches off until power or EN cycle. For the MAX14573 (continuous), the device only disables while the temperature is over the limit. There is no blanking time for thermal protection.

#### Overvoltage Lockout (OVLO)

The devices have a 33V (typ) preset OVLO threshold when the voltage at OVLO is set below the external OVLO select voltage ( $V_{OVLOSEL}$ ). Connect OVLO to GND to activate the preset OVLO threshold. Connect the external resistors to the OVLO pin as shown in the <u>Typical Operating Circuit</u> to externally adjust the OVLO threshold. Use the following equation to adjust the OVLO threshold. The recommended value for R3 is  $2.2M\Omega$ :

$$V_{OVLO} = V_{BG} \times \left[ 1 + \frac{R3}{R4} \right]$$

#### **Undervoltage Lockout (UVLO)**

The devices have a 19.2V (typ) preset UVLO threshold when the voltage at UVLO is set below the external UVLO select voltage ( $V_{UVLOSEL}$ ). Connect UVLO to GND to activate the preset UVLO threshold. Connect the external resistors to the UVLO pin as shown in the <u>Typical Operating Circuit</u> to externally adjust the UVLO threshold. Use the following equation to adjust the UVLO threshold. The recommended value for R1 is  $2.2M\Omega$ :

$$V_{UVLO} = V_{BG} \times \left[ 1 + \frac{R1}{R2} \right]$$

#### **Switch Control**

There are two independent enable inputs ( $\overline{HVEN}$  and EN) for the devices.  $\overline{HVEN}$  is a high-voltage-capable input. Toggle  $\overline{HVEN}$  or EN to reset the fault condition once a short circuit is detected and the devices shut down (Table 1).

#### **Input Debounce Protection**

The ICs feature input debounce protection. When the input voltage is higher than the UVLO threshold voltage for a period greater than the debounce time ( $t_{DEB}$ ), the internal FETs are turned on. This feature is intended for applications where the EN or  $\overline{HVEN}$  signal is present when the power supply ramps up (Figure 4).

### **Applications Information**

#### **Setting the Current Limit/Threshold**

A resistor from SETI to ground programs the current limit/threshold value for the devices. Leaving SETI unconnected selects a 0A current limit/threshold. Connecting SETI to ground asserts  $\overline{\text{FLAG}}$ . Use the following formula to calculate the current limit:

$$R_{SETI}(k\Omega) = \frac{11500}{I_{LIM}(mA)}$$

#### **IN Bypass Capacitor**

Connect a minimum of  $1\mu F$  capacitor from IN to GND to limit the input voltage drop during momentary output short-circuit conditions. Larger capacitor values further reduce the voltage undershoot at the input.

#### **Hot-Plug IN**

In many system powering applications, an input-filtering capacitor is required to lower the radiated emission, enhance the ESD capability, etc. In hot-plug applications, parasitic cable inductance, along with the input capacitor, cause overshoot and ringing when the powered cable is connected to the input terminal.

This effect causes the protection device to see almost twice the applied voltage. A transient voltage suppressor (TVS) is often used for industrial applications to protect the system from these conditions. We recommend using a TVS that is capable of limiting surge to 40V (max) placed close to the input terminal.

**Table 1. Switch Control**

| HVEN | EN | SWITCH STATUS |

|------|----|---------------|

| 0    | 0  | On            |

| 1    | 0  | Off           |

| 0    | 1  | On            |

| 1    | 1  | On            |

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

#### **OUT Bypass Capacitor**

For stable operation over the full temperature range and over the entire programmable current-limit range, connect a 1µF ceramic capacitor from OUT to ground. Excessive output capacitance can cause a false overcurrent condition due to decreased dV/dt across the capacitor. Calculate the maximum capacitive load (C<sub>MAX</sub>) value that can be connected to OUT by using the following formula:

$$C_{MAX}(\mu F) = \frac{I_{LIM}(mA) \times t_{BLANK(MIN)} (ms)}{V_{INI}(V)}$$

For example, for  $V_{IN}$  = 24V,  $t_{BLANK}$  = 15ms, and  $I_{LIM}$  = 4.2A, C<sub>MAX</sub> equals 2625µF.

#### **Output Freewheeling Diode for Inductive Hard Short to Ground**

In applications that require protection form a sudden short to ground with an inductive load or long cable, a Schottky diode between the OUT terminal and ground is recommended. This is to prevent a negative spike on OUT due to the inductive kickback during a short-circuit event.

#### **Layout and Thermal Dissipation**

To optimize the switch response time to output shortcircuit conditions, it is very important to keep all traces as short as possible to reduce the effect of undesirable parasitic inductance. Place input and output capacitors as close as possible to the device (no more than 5mm). IN and OUT must be connected with wide short traces to the power bus. During normal operation, the power dissipa-

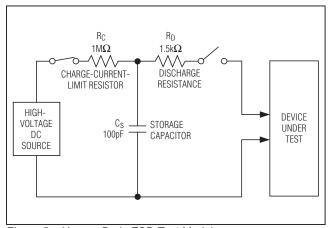

Figure 5a. Human Body ESD Test Model

tion is small and the package temperature change is minimal. If the output is continuously shorted to ground at the maximum supply voltage, the switches with the autoretry option do not cause thermal-shutdown detection to trip:

$$P_{(MAX)} = \frac{V_{IN(MAX)} \times I_{OUT(MAX)} \times t_{BLANK}}{t_{BETRY} + t_{BLANK}}$$

Attention must be given to the MAX14573 continuous current-limit version when the power dissipation during a fault condition can cause the device to reach the thermalshutdown threshold. Thermal vias from the exposed pad to ground plane are highly recommended to increase the system thermal capacitance while reducing the thermal resistance to the ambient.

#### **ESD Test Conditions**

The devices are specified for ±15kV (HBM) typical ESD resistance on IN when IN is bypassed to ground with a 1µF low-ESR ceramic capacitor. No capacitor is required for ±2kV (HBM) typical ESD on IN. All the pins have a ±2kV (HBM) typical ESD protection.

#### **HBM ESD Protection**

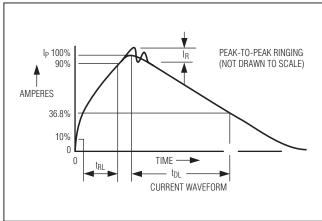

Figure 5a shows the Human Body Model, and Figure 5b shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$ resistor.

Figure 5b. Human Body Current Waveform

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

### **Ordering Information**

| PART                  | TEMP<br>RANGE     | PIN-<br>PACKAGE  | OVERCURRENT PROTECTION |

|-----------------------|-------------------|------------------|------------------------|

| <b>MAX14571</b> EUD+T | -40°C to<br>+85°C | 14 TSSOP-<br>EP* | Autoretry              |

| MAX14571EUD/V+T       | -40°C to<br>+85°C | 14 TSSOP-<br>EP* | Autoretry              |

| <b>MAX14572</b> EUD+T | -40°C to<br>+85°C | 14 TSSOP-<br>EP* | Latchoff               |

| <b>MAX14573</b> EUD+T | -40°C to<br>+85°C | 14 TSSOP-<br>EP* | Continuous             |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Chip Information**

PROCESS: BICMOS

Maxim Integrated | 13 www.maximintegrated.com

T = Tape and reel.

\*EP = Exposed pad.

N denotes an automotive qualified part.

# Adjustable Overvoltage and Overcurrent Protectors with High Accuracy

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                       | PAGES<br>CHANGED   |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 0                  | 9/12          | Initial release                                                                                                                                                                                                                   | _                  |

| 1                  | 12/12         | Removed future product asterisk and notes for the MAX14571/MAX14573, style edits.                                                                                                                                                 | 1–6, 8, 10, 11, 14 |

| 2                  | 1/15          | Updated Benefits and Features section                                                                                                                                                                                             | 1                  |

| 3                  | 6/16          | Updated Functional Diagram                                                                                                                                                                                                        | 9                  |

| 4                  | 7/17          | Updated Hot-Plug IN section, and added MAX14571EUD/V+T to the Ordering Information table. Corrections to SETI in the Typical Operating Circuit, HVEN in Benefits and Features, and RSETI in the Electrical Characteristics table. | 1, 2–4, 11, 14     |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.